hwtLib.structManipulators package¶

Submodules¶

hwtLib.structManipulators.arrayBuff_writer module¶

- class hwtLib.structManipulators.arrayBuff_writer.ArrayBuff_writer(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitWrite data in to a circula buffer allocated as an array. Collect items and send them over wDatapump when buffer is full or on timeout Maximum overlap of transactions is 1

items -> buff -> internal logic -> axi datapump

- HDL params

ID_WIDTH - default value 4 of type int

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

MAX_LEN - default value 15 of type int

USE_STRB - default value True of type bool

ID - default value 3 of type int

ITEM_WIDTH - default value 16 of type int

BUFF_DEPTH - default value 16 of type int

TIMEOUT - default value 1024 of type int

ITEMS - default value 512 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

items - of type hwt.interfaces.std.Handshaked - SLAVE

wDatapump - of type hwtLib.amba.datapump.intf.AxiWDatapumpIntf - MASTER

uploaded - of type hwt.interfaces.std.Signal with dtype=<Bits, 16bits> - MASTER

baseAddr - of type hwt.interfaces.std.RegCntrl - SLAVE

buff_remain - of type hwt.interfaces.std.Signal with dtype=<Bits, 16bits> - MASTER

- HDL components

buff - of type hwtLib.handshaked.fifo.HandshakedFifo

hwtLib.structManipulators.arrayItemGetter module¶

- class hwtLib.structManipulators.arrayItemGetter.ArrayItemGetter(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitGet specific item from array by index

- HDL params

ITEMS - default value 32 of type int

ITEM_WIDTH - default value 32 of type int

ID - default value 0 of type int

ID_WIDTH - default value 4 of type int

DATA_WIDTH - default value 64 of type int

ADDR_WIDTH - default value 32 of type int

MAX_TRANS_OVERLAP - default value 16 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

base - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - SLAVE

index - of type hwt.interfaces.std.Handshaked - SLAVE

item - of type hwt.interfaces.std.Handshaked - MASTER

rDatapump - of type hwtLib.amba.datapump.intf.AxiRDatapumpIntf - MASTER

- HDL components

itemSubIndexFifo - of type hwtLib.handshaked.fifo.HandshakedFifo

hwtLib.structManipulators.cLinkedListReader module¶

- class hwtLib.structManipulators.cLinkedListReader.CLinkedListReader(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitThis unit reads items from (circular) linked list like structure

struct node { item_t items[ITEMS_IN_BLOCK], struct node * next; };

synchronization is obtained by rdPtr/wrPtr (tail/head) pointer baseAddr is address of actual node

- HDL params

ID_WIDTH - default value 4 of type int

ID - default value 3 of type int

ID_LAST - default value 4 of type int

BUFFER_CAPACITY - default value 32 of type int

ITEMS_IN_BLOCK - default value 511 of type int

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

PTR_WIDTH - default value 16 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

rDatapump - of type hwtLib.amba.datapump.intf.AxiRDatapumpIntf - MASTER

dataOut - of type hwt.interfaces.std.Handshaked - MASTER

inBlockRemain - of type hwt.interfaces.std.Signal with dtype=<Bits, 9bits> - MASTER

baseAddr - of type hwt.interfaces.std.RegCntrl - SLAVE

rdPtr - of type hwt.interfaces.std.RegCntrl - SLAVE

wrPtr - of type hwt.interfaces.std.RegCntrl - SLAVE

- HDL components

dataFifo - of type hwtLib.handshaked.fifo.HandshakedFifo

hwtLib.structManipulators.cLinkedListWriter module¶

- class hwtLib.structManipulators.cLinkedListWriter.CLinkedListWriter(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitThis unit writes items to (circular) linked list like structure (List does not necessary need to be circular but space is specified by two pointers like in circular queue)

struct node { item_t items[ITEMS_IN_BLOCK], struct node * next; };

synchronization is obtained by rdPtr/wrPtr (tail/head) pointer baseAddr is address of actual node

- HDL params

ID_WIDTH - default value 4 of type int

ID - default value 3 of type int

BUFFER_CAPACITY - default value 32 of type int

ITEMS_IN_BLOCK - default value 511 of type int

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

PTR_WIDTH - default value 16 of type int

TIMEOUT - default value 4096 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

rDatapump - of type hwtLib.amba.datapump.intf.AxiRDatapumpIntf - MASTER

wDatapump - of type hwtLib.amba.datapump.intf.AxiWDatapumpIntf - MASTER

dataIn - of type hwt.interfaces.std.Handshaked - SLAVE

baseAddr - of type hwt.interfaces.std.RegCntrl - SLAVE

rdPtr - of type hwt.interfaces.std.RegCntrl - SLAVE

wrPtr - of type hwt.interfaces.std.RegCntrl - SLAVE

- HDL components

dataFifo - of type hwtLib.handshaked.fifo.HandshakedFifo

- baseAddrLogic(nextBlockTransition_in)[source]¶

Logic for downloading address of next block

- Parameters

nextBlockTransition_in – signal which means that baseIndex should be changed to nextBaseIndex if nextBaseAddrReady is not high this signal has no effect (= regular handshake)

- Returns

(baseIndex, nextBaseIndex, nextBaseReady is ready and nextBlockTransition_in can be used)

hwtLib.structManipulators.mmu_2pageLvl module¶

- class hwtLib.structManipulators.mmu_2pageLvl.MMU_2pageLvl(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitMMU where parent page table is stored in ram this unit and only items from leaf page tables are download on each request over rDatapump interface

- HDL params

ID_WIDTH - default value 1 of type int

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

VIRT_ADDR_WIDTH - default value 32 of type int

LVL1_PAGE_TABLE_ITEMS - default value 512 of type int

PAGE_SIZE - default value 4096 of type int

MAX_OVERLAP - default value 16 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

rDatapump - of type hwtLib.amba.datapump.intf.AxiRDatapumpIntf - MASTER

virtIn - of type hwt.interfaces.std.Handshaked - SLAVE

physOut - of type hwt.interfaces.std.Handshaked - MASTER

segfault - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

lvl1Table - of type hwt.interfaces.std.BramPort_withoutClk - SLAVE

- HDL components

lvl1Storage - of type hwtLib.mem.ram.RamSingleClock

lvl1Converter - of type hwtLib.handshaked.ramAsHs.RamAsHs

lvl2get - of type hwtLib.structManipulators.arrayItemGetter.ArrayItemGetter

lvl2indxFifo - of type hwtLib.handshaked.fifo.HandshakedFifo

pageOffsetFifo - of type hwtLib.handshaked.fifo.HandshakedFifo

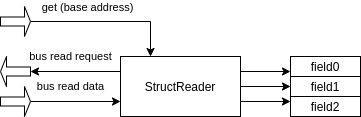

hwtLib.structManipulators.structReader module¶

- class hwtLib.structManipulators.structReader.StructReader(structT, tmpl=None, frames=None)[source]¶

Bases:

AxiS_frameParserThis unit downloads required structure fields over rDatapump interface from address specified by get interface

- Variables

~.ID – Param, id for transactions on bus

~.READ_ACK – Param, if true ready on “get” will be set only when component is in idle (if false “get” is regular handshaked interface)

~.SHARED_READY – Param, if this is true field interfaces will be of type VldSynced and single ready signal will be used for all else every interface will be instance of Handshaked and it will have it’s own ready(rd) signal

- HDL params

ID - default value 0 of type int

ID_WIDTH - default value 0 of type int

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

MAX_BYTES - default value 4096 of type int

USE_STRB - default value False of type bool

READ_ACK - default value False of type bool

SHARED_READY - default value False of type bool

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataOut - of type hwt.interfaces.structIntf.StructIntf with dtype=struct { <Bits, 64bits, unsigned> item0 //<Bits, 64bits, unsigned> empty space <Bits, 64bits, unsigned> item1 //<Bits, 64bits, unsigned> empty space <Bits, 16bits, unsigned> item2 <Bits, 16bits, unsigned> item3 <Bits, 32bits, unsigned> item4 //<Bits, 32bits, unsigned> empty space <Bits, 64bits, unsigned> item5 //<Bits, 32bits, unsigned> empty space //<Bits, 64bits, unsigned> empty space //<Bits, 64bits, unsigned> empty space //<Bits, 64bits, unsigned> empty space <Bits, 64bits, unsigned> item6 <Bits, 64bits, unsigned> item7 } - MASTER

get - of type hwt.interfaces.std.Handshaked - SLAVE

rDatapump - of type hwtLib.amba.datapump.intf.AxiRDatapumpIntf - MASTER

- HDL components

parser - of type hwtLib.amba.axis_comp.frame_parser._parser.AxiS_frameParser

gen_get_reg_0 - of type hwtLib.handshaked.reg.HandshakedReg

- __init__(structT, tmpl=None, frames=None)[source]¶

- Parameters

structT – instance of HStruct which specifies data format to download

tmpl – instance of TransTmpl for this structT

frames – list of FrameTmpl instances for this tmpl

- Note

if tmpl and frames are None they are resolved from structT parseTemplate

- Note

this unit can parse sequence of frames, if they are specified by “frames”

- Attention

interfaces for each field in struct will be dynamically created

- Attention

structT can not contain fields with variable size like HStream

- driveReqRem(req: AddrSizeHs, MAX_BITS: int)[source]¶

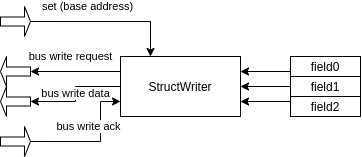

hwtLib.structManipulators.structWriter module¶

- class hwtLib.structManipulators.structWriter.StructWriter(structT, tmpl=None, frames=None)[source]¶

Bases:

StructReaderWrite struct specified in constructor over wDatapump interface on address specified over set interface

- Variables

~.MAX_OVERLAP – parameter which specifies the maximum number of concurrent transaction

~.WRITE_ACK – Param, if true ready on “set” will be set only when component is in idle (if false “set” is regular handshaked interface)

- HDL params

ID - default value 0 of type int

ID_WIDTH - default value 0 of type int

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

MAX_BYTES - default value 4096 of type int

USE_STRB - default value False of type bool

READ_ACK - default value False of type bool

SHARED_READY - default value False of type bool

MAX_OVERLAP - default value 2 of type int

WRITE_ACK - default value False of type bool

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataIn - of type hwt.interfaces.structIntf.StructIntf with dtype=struct { <Bits, 64bits, unsigned> item0 //<Bits, 64bits, unsigned> empty space <Bits, 64bits, unsigned> item1 //<Bits, 64bits, unsigned> empty space <Bits, 16bits, unsigned> item2 <Bits, 16bits, unsigned> item3 <Bits, 32bits, unsigned> item4 //<Bits, 32bits, unsigned> empty space <Bits, 64bits, unsigned> item5 //<Bits, 32bits, unsigned> empty space //<Bits, 64bits, unsigned> empty space //<Bits, 64bits, unsigned> empty space //<Bits, 64bits, unsigned> empty space <Bits, 64bits, unsigned> item6 <Bits, 64bits, unsigned> item7 } - SLAVE

set - of type hwt.interfaces.std.Handshaked - SLAVE

writeAck - of type hwt.interfaces.std.HandshakeSync - MASTER

wDatapump - of type hwtLib.amba.datapump.intf.AxiWDatapumpIntf - MASTER

- HDL components

frameAssember - of type hwtLib.amba.axis_comp.frame_deparser._deparser.AxiS_frameDeparser

ackPropageteInfo - of type hwtLib.handshaked.fifo.HandshakedFifo

gen_set_reg_0 - of type hwtLib.handshaked.reg.HandshakedReg