hwtLib.mem package¶

A package dedicated to a memory related components, interfaces and utilities.

Subpackages¶

Submodules¶

hwtLib.mem.bramPortEndpoint module¶

- class hwtLib.mem.bramPortEndpoint.BramPortEndpoint(structTemplate, intfCls=<class 'hwt.interfaces.std.BramPort_withoutClk'>, shouldEnterFn=None)[source]¶

Bases:

BusEndpointDelegate transaction from BrapmPort interface to interfaces for fields of specified structure.

- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 32 of type int

HAS_R - default value True of type bool

HAS_W - default value True of type bool

HAS_BE - default value False of type bool

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

bus - of type hwt.interfaces.std.BramPort_withoutClk - SLAVE

decoded - of type hwt.interfaces.structIntf.StructIntf with dtype=struct { <Bits, 32bits, unsigned> reg0 <Bits, 32bits, unsigned> reg1 <Bits, 32bits, unsigned>[1024] segment0 <Bits, 32bits, unsigned>[1024] segment1 <Bits, 32bits, unsigned>[1028] nonAligned0 } - MASTER

- __init__(structTemplate, intfCls=<class 'hwt.interfaces.std.BramPort_withoutClk'>, shouldEnterFn=None)[source]¶

- Parameters

structTemplate – instance of HStruct which describes address space of this endpoint

intfCls – class of bus interface which should be used

shouldEnterFn – function(root_t, structFieldPath) return (shouldEnter, shouldUse) where shouldEnter is flag that means iterator over this interface should look inside of this actual object and shouldUse flag means that this field should be used (to create interface)

- _getAddrStep()¶

- Returns

how many bits is one unit of address (e.g. 8 bits for char * pointer, 36 for 36 bit bram)

- _getWordAddrStep()¶

- Returns

size of one word in unit of address

hwtLib.mem.bramPortSimMemSpaceMaster module¶

- class hwtLib.mem.bramPortSimMemSpaceMaster.BramPortSimMemSpaceMaster(bus, registerMap)[source]¶

Bases:

AbstractMemSpaceMasterController of BramPort simulation agent which keeps track of transactions and allows struct like data access

hwtLib.mem.cam module¶

- class hwtLib.mem.cam.Cam(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitContent addressable memory. MATCH_LATENCY = 1

- HDL params

KEY_WIDTH - default value 15 of type int

ITEMS - default value 32 of type int

USE_VLD_BIT - default value True of type boolif true the validity bit is a part of the CAM record

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

match - of type hwt.interfaces.std.Handshaked - SLAVE

out - of type hwt.interfaces.std.Handshaked - MASTER

write - of type hwtLib.common_nonstd_interfaces.addr_data_hs.AddrDataVldHs - SLAVE

- matchHandler(mem, key: Handshaked, match_res: Handshaked)[source]¶

- class hwtLib.mem.cam.CamMultiPort(hdl_name_override: Optional[str] = None)[source]¶

Bases:

CamA variant of

Camwith multiple ports for lookup- HDL params

KEY_WIDTH - default value 15 of type int

ITEMS - default value 32 of type int

USE_VLD_BIT - default value True of type bool

MATCH_PORT_CNT - default value 2 of type intnumber of CAM ports for matching, if None there is only as single port otherwise there is an array of such a ports of specified size

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

match_0 - of type hwt.interfaces.std.Handshaked - SLAVE

match_1 - of type hwt.interfaces.std.Handshaked - SLAVE

out_0 - of type hwt.interfaces.std.Handshaked - MASTER

out_1 - of type hwt.interfaces.std.Handshaked - MASTER

write - of type hwtLib.common_nonstd_interfaces.addr_data_hs.AddrDataVldHs - SLAVE

- matchHandler(mem, key: Handshaked, match_res: Handshaked)[source]¶

hwtLib.mem.cuckooHashTablWithRam module¶

- class hwtLib.mem.cuckooHashTablWithRam.CuckooHashTableWithRam(polynomials)[source]¶

Bases:

CuckooHashTableA cuckoo hash table core with integrated memory

- HDL params

TABLE_SIZE - default value 32 of type int

DATA_WIDTH - default value 32 of type int

KEY_WIDTH - default value 8 of type int

LOOKUP_KEY - default value False of type bool

TABLE_CNT - default value 2 of type int

MAX_LOOKUP_OVERLAP - default value 16 of type int

MAX_REINSERT - default value 15 of type int

POLYNOMIALS - default value (<class ‘hwtLib.logic.crcPoly.CRC_32’>, <class ‘hwtLib.logic.crcPoly.CRC_32C’>) of type tuple

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

insert - of type hwtLib.mem.cuckooHashTable_intf.CInsertIntf - SLAVE

insertRes - of type hwtLib.mem.cuckooHashTable_intf.CInsertResIntf - MASTER

lookup - of type hwtLib.mem.hashTable_intf.LookupKeyIntf - SLAVE

lookupRes - of type hwtLib.mem.hashTable_intf.LookupResultIntf - MASTER

delete - of type hwtLib.mem.cuckooHashTable_intf.CInsertIntf - SLAVE

clean - of type hwt.interfaces.std.HandshakeSync - SLAVE

- HDL components

table_cores_0 - of type hwtLib.mem.hashTableCoreWithRam.HashTableCoreWithRam

table_cores_1 - of type hwtLib.mem.hashTableCoreWithRam.HashTableCoreWithRam

gen_lookupRes_reg_0 - of type hwtLib.handshaked.reg.HandshakedReg

gen_lookupRes_reg_1 - of type hwtLib.handshaked.reg.HandshakedReg

hwtLib.mem.cuckooHashTable module¶

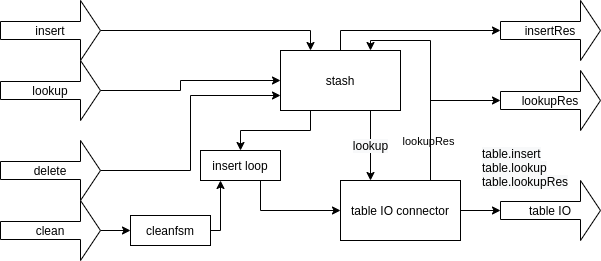

- class hwtLib.mem.cuckooHashTable.CuckooHashTable[source]¶

Bases:

HashTableCoreCuckoo hash uses more tables with different hash functions

Lookup is performed in all tables at once and if item is found in any table. The item is found. Otherwise item is not in tables. lookup time: O(1)

Insert has to first lookup if item is in any table. If any table contains invalid item. The item is stored there and insert operation is complete. If there was a valid item under this key in all tables. One is selected and it is swapped with current item. Insert process then repeats with this item. Until some invalid item (empty slot) is found.

Inserting into table does not have to be successful and in this case, fsm ends up in infinite loop and it will be reinserting items for ever. insert time: O(inf)

- HDL params

TABLE_SIZE - default value 32 of type int

DATA_WIDTH - default value 32 of type int

KEY_WIDTH - default value 8 of type int

LOOKUP_KEY - default value False of type bool

TABLE_CNT - default value 2 of type int

MAX_LOOKUP_OVERLAP - default value 16 of type int

MAX_REINSERT - default value 15 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

insert - of type hwtLib.mem.cuckooHashTable_intf.CInsertIntf - SLAVE

insertRes - of type hwtLib.mem.cuckooHashTable_intf.CInsertResIntf - MASTER

lookup - of type hwtLib.mem.hashTable_intf.LookupKeyIntf - SLAVE

lookupRes - of type hwtLib.mem.hashTable_intf.LookupResultIntf - MASTER

delete - of type hwtLib.mem.cuckooHashTable_intf.CInsertIntf - SLAVE

clean - of type hwt.interfaces.std.HandshakeSync - SLAVE

tables_0 - of type hwtLib.mem.hashTable_intf.HashTableIntf - MASTER

tables_1 - of type hwtLib.mem.hashTable_intf.HashTableIntf - MASTER

- configure_tables(tables: List[HashTableCore])[source]¶

share the configuration with the table engines

- lookupRes_driver(state: RtlSignal, lookupFoundOH: RtlSignal)[source]¶

If lookup request comes from external interface “lookup” propagate results from tables to “lookupRes”.

- stash_load(isIdle, lookupResNext, insertTargetOH, stash, lookup_not_in_progress, another_lookup_possible)[source]¶

load a stash register from lookup/insert/delete interface

- tables_insert_driver(state: RtlSignal, insertTargetOH: RtlSignal, insertIndex: RtlSignal, stash: RtlSignal)[source]¶

- Parameters

state – state register of main FSM

insertTargetOH – index of table where insert should be performed, one hot encoding

insertIndex – address for table where item should be placed

stash – stash register with data for insert/lookup/delete from table

hwtLib.mem.cuckooHashTable_intf module¶

- class hwtLib.mem.cuckooHashTable_intf.CInsertIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

HandshakeSyncCuckoo hash insert interface

- class hwtLib.mem.cuckooHashTable_intf.CInsertIntfAgent(sim, intf)[source]¶

Bases:

HandshakedAgentAgent for CInsertIntf interface

- class hwtLib.mem.cuckooHashTable_intf.CInsertResIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

CInsertIntfAn interface with an result of insert operation.

- Variables

pop – signal if 1 the key and data on this interface contains the item which had to be removed during insert because the insertion limit was exceeded

hwtLib.mem.fifo module¶

- class hwtLib.mem.fifo.Fifo(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitGeneric FIFO usually mapped to BRAM.

- Variables

~.EXPORT_SIZE – parameter, if true “size” signal will be exported

~.size – optional signal with count of items stored in this fifo

~.EXPORT_SPACE – parameter, if true “space” signal is exported

~.space – optional signal with count of items which can be added to this fifo

- HDL params

DATA_WIDTH - default value 8 of type int

DEPTH - default value 16 of type int

EXPORT_SIZE - default value True of type bool

EXPORT_SPACE - default value True of type bool

INIT_DATA - default value (1, 2, 3) of type tuple

INIT_DATA_FIRST_WORD - default value 0 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataIn - of type hwt.interfaces.std.FifoWriter - SLAVE

dataOut - of type hwt.interfaces.std.FifoReader - MASTER

size - of type hwt.interfaces.std.Signal with dtype=<Bits, 5bits, unsigned> - MASTER

space - of type hwt.interfaces.std.Signal with dtype=<Bits, 5bits, unsigned> - MASTER

- fifo_pointers(DEPTH: int, write_en_wait: Tuple[RtlSignal, RtlSignal], read_en_wait_list: List[Tuple[RtlSignal, RtlSignal]]) List[Tuple[RtlSignal, RtlSignal]][source]¶

Create fifo writer and reader pointers and enable/wait logic This functions supports multiple reader pointers

- Attention

writer pointer next logic check only last reader pointer

- Returns

list, tule(en, ptr) for writer and each reader

hwtLib.mem.fifoArray module¶

- class hwtLib.mem.fifoArray.FifoArray(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitThis component is an array of list nodes, which can be used to emulate multiple FIFOs. The memory is shared and the number of lists stored in this array is limited only by memory.

Corresponds to data structure:

// note that in implementation each part of struct item is stored in separate array struct item { value_t value; item * next; bool valid; bool last; }; item items[ITEMS];

- HDL params

ITEMS - default value 4 of type int

DATA_WIDTH - default value 8 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

insert - of type hwtLib.mem.fifoArray.FifoArrayInsertInterface - SLAVE

pop - of type hwtLib.mem.fifoArray.FifoArrayPopInterface - MASTER

- class hwtLib.mem.fifoArray.FifoArrayInsertInterface(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

HandshakedBiDirectional- Variables

~.append – if append = 1 the item is appended to last list item specified using “addr” else new list is created and “addr” value is ignored

~.addr – an address with potential end of the list

~.data – data to store in next list node

~.addr_ret – an address where the item was inserted to

- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 32 of type int

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

append - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

addr_ret - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - SLAVE (Master=IN)

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

- class hwtLib.mem.fifoArray.FifoArrayInsertInterfaceAgent(sim, intf)[source]¶

Bases:

HandshakedBiDirectionalAgentSimulation agent for

FifoArrayInsertInterfaceinterface

- class hwtLib.mem.fifoArray.FifoArrayPopInterface(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

AddrInDataOutHs- Variables

~.addr – the address of the list head to read from:

~.data – the return data which was read

~.last – flag which tell if this node was last in this list and thus this list is now empty and deallocated

~.addr_next – address on a next item in this FIFO

- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 32 of type int

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - SLAVE (Master=IN)

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

last - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

addr_next - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

- class hwtLib.mem.fifoArray.FifoArrayPopInterfaceAgent(sim, intf)[source]¶

Bases:

AddrInDataOutHsAgentSimulation agent for

FifoArrayPopInterfaceAgentinterface

hwtLib.mem.fifoAsync module¶

- class hwtLib.mem.fifoAsync.FifoAsync(hdl_name_override: Optional[str] = None)[source]¶

Bases:

FifoAsynchronous fifo using BRAM/LUT memory, based on: * https://github.com/ZipCPU/website/blob/master/examples/afifo.v * https://github.com/alexforencich/verilog-axis/blob/master/rtl/axis_async_fifo.v

- HDL params

DATA_WIDTH - default value 64 of type int

DEPTH - default value 4 of type int

EXPORT_SIZE - default value False of type bool

EXPORT_SPACE - default value False of type bool

INIT_DATA - default value () of type tuple

INIT_DATA_FIRST_WORD - default value <class ‘hwt.synthesizer.rtlLevel.constants.NOT_SPECIFIED’> of type type

IN_FREQ - default value 100000000 of type int

OUT_FREQ - default value 100000000 of type int

- HDL IO

dataIn_clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

dataOut_clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

dataIn_rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataIn - of type hwt.interfaces.std.FifoWriter - SLAVE

dataOut_rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataOut - of type hwt.interfaces.std.FifoReader - MASTER

hwtLib.mem.fifoCopy module¶

- class hwtLib.mem.fifoCopy.FifoCopy(hdl_name_override: Optional[str] = None)[source]¶

Bases:

FifoFifo with an extra signals to control replay of lastly stored data

- HDL params

DATA_WIDTH - default value 8 of type int

DEPTH - default value 16 of type int

EXPORT_SIZE - default value False of type bool

EXPORT_SPACE - default value False of type bool

INIT_DATA - default value () of type tuple

INIT_DATA_FIRST_WORD - default value <class ‘hwt.synthesizer.rtlLevel.constants.NOT_SPECIFIED’> of type type

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataIn - of type hwt.interfaces.std.FifoWriter - SLAVE

dataOut - of type hwt.interfaces.std.FifoReader - MASTER

dataOut_copy_frame - of type hwt.interfaces.std.VldSynced - SLAVE The channel which drives when to capture start of the frame and when to start relaying previously stored frame from the marked start

hwtLib.mem.fifoDrop module¶

- class hwtLib.mem.fifoDrop.FifoDrop(hdl_name_override: Optional[str] = None)[source]¶

Bases:

FifoFifo with an extra signals for writter which allows to commit or discard data chung writen in to fifo.

- HDL params

DATA_WIDTH - default value 8 of type int

DEPTH - default value 16 of type int

EXPORT_SIZE - default value True of type bool

EXPORT_SPACE - default value True of type bool

INIT_DATA - default value () of type tuple

INIT_DATA_FIRST_WORD - default value <class ‘hwt.synthesizer.rtlLevel.constants.NOT_SPECIFIED’> of type type

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataIn - of type hwtLib.mem.fifoDrop.FifoWriterDropable - SLAVE

dataOut - of type hwt.interfaces.std.FifoReader - MASTER

size - of type hwt.interfaces.std.Signal with dtype=<Bits, 5bits, unsigned> - MASTER

space - of type hwt.interfaces.std.Signal with dtype=<Bits, 5bits, unsigned> - MASTER

- class hwtLib.mem.fifoDrop.FifoWriterDropable(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

FifoWriterFIFO write port interface witch commit and discard signal used to drop data chunks already written in fifo

- Variables

~.commit – if 1 all the written data are made available to reader, including current data word

~.discard – if 1 all written data which were not commited are discarded includeing current data word

- HDL params

DATA_WIDTH - default value 8 of type int

- HDL IO

en - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

wait - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

commit - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

discard - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

- class hwtLib.mem.fifoDrop.FifoWriterDropableAgent(sim: HdlSimulator, intf, allowNoReset=False)[source]¶

Bases:

FifoWriterAgent

hwtLib.mem.hashTableCore module¶

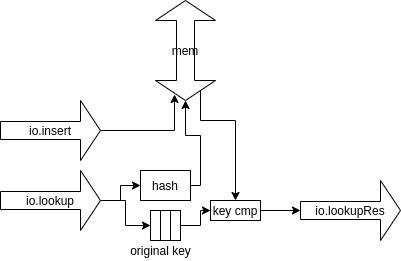

- class hwtLib.mem.hashTableCore.HashTableCore(polynome)[source]¶

Bases:

UnitGeneric hash table, in block RAM there is a input key which is hashed ad this has is used as an index into memory item on this place is checked and returned on “lookupRes” interface (item does have to be found, see “found” flag in LookupResultIntf)

memory is an array of items in format

struct item { bool item_vld; data_t data; key_t key; };

- Variables

~.ITEMS_CNT – number of items in memory of hash table

~.KEY_WIDTH – width of the key used by hash table

~.DATA_WIDTH – width of data, can be zero and then no data interface is instantiated

~.LOOKUP_ID_WIDTH – width of id signal for lookup (tag used only by parent component to mark this lookup for later result processing, can be 0)

~.LOOKUP_HASH – flag if lookup interface should have hash signal

~.LOOKUP_KEY – flag if lookup interface should have key signal

~.POLYNOME – polynome for crc hash used in this table

- HDL params

ITEMS_CNT - default value 32 of type int

KEY_WIDTH - default value 16 of type int

DATA_WIDTH - default value 8 of type int

LOOKUP_ID_WIDTH - default value 0 of type int

LOOKUP_HASH - default value False of type bool

LOOKUP_KEY - default value False of type bool

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

io - of type hwtLib.mem.hashTable_intf.HashTableIntf - SLAVE

r - of type hwtLib.handshaked.ramAsHs.RamHsR - MASTER

w - of type hwtLib.common_nonstd_interfaces.addr_data_hs.AddrDataHs - MASTER

- HDL components

hash - of type hwtLib.logic.crcComb.CrcComb

gen_origKeyIn_reg_0 - of type hwtLib.handshaked.reg.HandshakedReg

- insertLogic(ramW: AddrDataHs)[source]¶

hwtLib.mem.hashTableCoreWithRam module¶

- class hwtLib.mem.hashTableCoreWithRam.HashTableCoreWithRam(polynome)[source]¶

Bases:

HashTableCore- HDL params

ITEMS_CNT - default value 32 of type int

KEY_WIDTH - default value 16 of type int

DATA_WIDTH - default value 8 of type int

LOOKUP_ID_WIDTH - default value 0 of type int

LOOKUP_HASH - default value False of type bool

LOOKUP_KEY - default value False of type bool

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

io - of type hwtLib.mem.hashTable_intf.HashTableIntf - SLAVE

- HDL components

hash - of type hwtLib.logic.crcComb.CrcComb

table - of type hwtLib.mem.ram.RamSingleClock

tableConnector - of type hwtLib.handshaked.ramAsHs.RamAsHs

gen_origKeyIn_reg_0 - of type hwtLib.handshaked.reg.HandshakedReg

hwtLib.mem.hashTable_intf module¶

- class hwtLib.mem.hashTable_intf.HashTableIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

Interface- HDL params

ITEMS_CNT - default value 32 of type int

KEY_WIDTH - default value 16 of type int

DATA_WIDTH - default value 8 of type int

LOOKUP_ID_WIDTH - default value 0 of type int

LOOKUP_HASH - default value False of type bool

LOOKUP_KEY - default value False of type bool

- HDL IO

insert - of type hwtLib.mem.hashTable_intf.InsertIntf - MASTER

lookup - of type hwtLib.mem.hashTable_intf.LookupKeyIntf - MASTER

lookupRes - of type hwtLib.mem.hashTable_intf.LookupResultIntf - SLAVE (Master=IN)

- class hwtLib.mem.hashTable_intf.HashTableIntfAgent(sim: HdlSimulator, intf: HashTableIntf)[source]¶

Bases:

AgentBase- __init__(sim: HdlSimulator, intf: HashTableIntf)[source]¶

- class hwtLib.mem.hashTable_intf.InsertIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

HandshakeSync- HDL params

HASH_WIDTH - default value 8 of type int

KEY_WIDTH - default value 8 of type int

DATA_WIDTH - default value 0 of type int

- HDL IO

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

hash - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

key - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

item_vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

- class hwtLib.mem.hashTable_intf.InsertIntfAgent(sim: HdlSimulator, intf: InsertIntf)[source]¶

Bases:

HandshakedAgentSimulation agent for .InsertIntf interface

- data format:

if interface has data signal, data format is tuple (hash, key, data, item_vld)

if interface does not have data signal, data format is tuple (hash, key, item_vld)

- __init__(sim: HdlSimulator, intf: InsertIntf)[source]¶

- Parameters

rst – tuple (rst signal, rst_negated flag)

- class hwtLib.mem.hashTable_intf.LookupKeyIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

HandshakeSync- HDL params

LOOKUP_ID_WIDTH - default value 0 of type int

KEY_WIDTH - default value 8 of type int

- HDL IO

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

key - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

- class hwtLib.mem.hashTable_intf.LookupKeyIntfAgent(sim: HdlSimulator, intf: LookupKeyIntf)[source]¶

Bases:

HandshakedAgentSimulation agent for LookupKeyIntf interface

- __init__(sim: HdlSimulator, intf: LookupKeyIntf)[source]¶

- Parameters

rst – tuple (rst signal, rst_negated flag)

- class hwtLib.mem.hashTable_intf.LookupResultIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

HandshakedInterface for result of lookup in hash table

- Variables

~.HASH_WIDTH – width of the hash used by hash table

~.KEY_WIDTH – width of the key used by hash table

~.LOOKUP_HASH – flag if this interface should have hash signal

~.LOOKUP_KEY – flag if this interface should have hash signal

~.hash – hash for this key (= index in this table)

~.key – original key which was searched for

~.data – data under this key

~.occupied – flag which tells if there is an valid item under this key

- HDL params

HASH_WIDTH - default value 8 of type int

KEY_WIDTH - default value 8 of type int

DATA_WIDTH - default value 0 of type int

LOOKUP_ID_WIDTH - default value 0 of type int

LOOKUP_HASH - default value False of type bool

LOOKUP_KEY - default value False of type bool

- HDL IO

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

found - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

occupied - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

- class hwtLib.mem.hashTable_intf.LookupResultIntfAgent(sim, intf)[source]¶

Bases:

HandshakedAgentSimulation agent for .LookupResultIntf data is stored in .data data format is tuple (hash, key, data, found) but some items can be missing depending on configuration of interface

hwtLib.mem.lutRam module¶

hwtLib.mem.ram module¶

- class hwtLib.mem.ram.RamMultiClock(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitRAM where each port has an independet clock. It can be configured to true dual port RAM etc. It can also be configured to have write mask or to be composed from multiple smaller memories.

- HDL params

ADDR_WIDTH - default value 10 of type int

DATA_WIDTH - default value 64 of type int

PORT_CNT - default value 2 of type int

HAS_BE - default value False of type bool

MAX_BLOCK_DATA_WIDTH - default value None of type None

INIT_DATA - default value None of type None

- HDL IO

port_0 - of type hwt.interfaces.std.BramPort - SLAVE

port_1 - of type hwt.interfaces.std.BramPort - SLAVE

- class hwtLib.mem.ram.RamSingleClock(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitRAM/ROM with only one clock signal. It can be configured to have arbitrary number of ports. It can also be configured to have write mask or to be composed from multiple smaller memories.

- HDL params

ADDR_WIDTH - default value 10 of type int

DATA_WIDTH - default value 64 of type int

PORT_CNT - default value 1 of type intParam which specifies number of ram ports, it can be int or tuple of READ_WRITE, WRITE, READ to specify rw access for each port separately

HAS_BE - default value False of type boolParam, if True the write ports will have byte enable signal

MAX_BLOCK_DATA_WIDTH - default value None of type None

INIT_DATA - default value None of type None

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

port_0 - of type hwt.interfaces.std.BramPort_withoutClk - SLAVE

- PORT_CLS¶

alias of

BramPort_withoutClk

- static connect_port(clk: RtlSignal, port: BramPort_withoutClk, mem: RtlSignal)[source]¶

- static mem_write(mem, port: BramPort_withoutClk)[source]¶

hwtLib.mem.ramCumulativeMask module¶

- class hwtLib.mem.ramCumulativeMask.BramPort_withReadMask_withoutClk(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

BramPort_withoutClkBlock RAM port with a

enhandshaked interface for arbitration- Variables

do_accumulate – Signal if 1 the mask bits are or-ed together with the value in stored in ram

do_overwrite – Signal if 1 the the data mask in ram is set to current we value

dout_mask – Read port contains this signal which contains the cumulative validity mask for the data.

- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

HAS_R - default value True of type bool

HAS_W - default value True of type bool

HAS_BE - default value False of type bool

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

din - of type hwt.interfaces.std.Signal with dtype=<Bits, 64bits> - MASTER

dout - of type hwt.interfaces.std.Signal with dtype=<Bits, 64bits> - SLAVE (Master=IN)

en - of type hwt.interfaces.std.HandshakeSync - MASTER

we - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

- class hwtLib.mem.ramCumulativeMask.RamCumulativeMask(hdl_name_override: Optional[str] = None)[source]¶

Bases:

RamSingleClockRAM which stores also byte enable value for each data word (to keep track of which bytes were updated).

- Note

BramPort_withReadMask_withoutClkcontains the informations about how to control this component.

- PORT_CLS¶

alias of

BramPort_withReadMask_withoutClk

hwtLib.mem.ramTransactional module¶

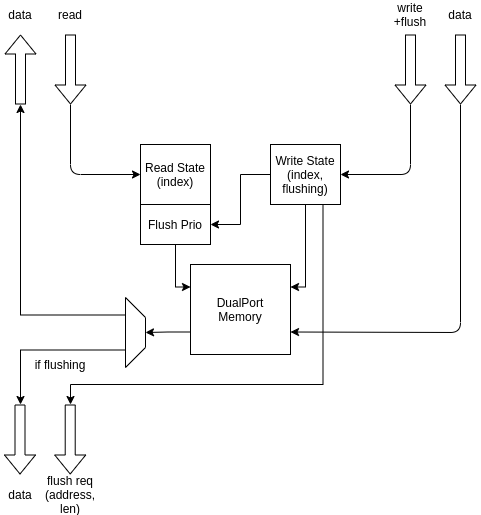

- class hwtLib.mem.ramTransactional.RamTransactional(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitA RAM with 1 read port and 1 write port with flush before functionality. If the flush is activate the current data is read first before it is overwritten by write data. This memory supports multiword transaction and the swap, read and write is atomic in relation with other transactions.

- HDL params

ADDR_WIDTH - default value 8 of type int

DATA_WIDTH - default value 8 of type int

WORD_WIDTH - default value 16 of type int

MAX_BLOCK_DATA_WIDTH - default value None of type None

W_PRIV_T - default value None of type None

R_ID_WIDTH - default value 0 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

r - of type hwtLib.mem.ramTransactional_io.TransRamHsR - SLAVE

w - of type hwtLib.mem.ramTransactional_io.TransRamHsW - SLAVE

flush_data - of type hwtLib.mem.ramTransactional_io.TransRamHsW - MASTER

- HDL components

data_array - of type hwtLib.mem.ram.RamSingleClock

data_arr_r_to_hs - of type hwtLib.handshaked.ramAsHs.RamAsHs

data_arr_w_to_hs - of type hwtLib.handshaked.ramAsHs.RamAsHs

r_meta_0 - of type hwtLib.handshaked.reg.HandshakedReg

r_meta_1 - of type hwtLib.handshaked.reg.HandshakedReg

- construct_r_meta(flush_req: RtlSignal, read_pending: RtlSignal, r: RamHsR, w: AddrDataHs, w_index: StructIntf, r_index_o: StructIntf) HandshakedReg[source]¶

- construct_ram_io() Tuple[RamHsR, AddrDataHs][source]¶

- construct_read_part(r: TransRamHsR, w_addr: RtlSignal, da_r: RamHsR, r_meta: List[HandshakedReg], flush_req: RtlSignal, read_pending: RtlSignal, r_index_o: StructIntf, r_index_i: StructIntf, flush_data: TransRamHsW)[source]¶

- construct_write_part(w: TransRamHsW, da_r: RamHsR, da_w: AddrDataHs, w_index_i: StructIntf, w_index_o, r_index_o, r_meta_din: HsStructIntf)[source]¶

hwtLib.mem.ramTransactional_io module¶

- class hwtLib.mem.ramTransactional_io.TransRamHsR(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

InterfaceHandshaked RAM port

- HDL params

DATA_WIDTH - default value 8 of type int

USE_STRB - default value True of type bool

ID_WIDTH - default value 0 of type int

ADDR_WIDTH - default value 32 of type int

- HDL IO

addr - of type hwtLib.mem.ramTransactional_io.TransRamHsR_addr - MASTER

data - of type hwtLib.amba.axis.AxiStream - SLAVE (Master=IN)

- class hwtLib.mem.ramTransactional_io.TransRamHsR_addr(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

HandshakeSync- HDL params

PRIV_T - default value None of type None

ADDR_WIDTH - default value 32 of type int

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

- class hwtLib.mem.ramTransactional_io.TransRamHsW(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

Interface- HDL params

DATA_WIDTH - default value 64 of type int

USE_STRB - default value True of type bool

PRIV_T - default value None of type None

ADDR_WIDTH - default value 32 of type int

USE_FLUSH - default value True of type bool

- HDL IO

addr - of type hwtLib.mem.ramTransactional_io.TransRamHsW_addr - MASTER

data - of type hwtLib.amba.axis.AxiStream - MASTER

- class hwtLib.mem.ramTransactional_io.TransRamHsW_addr(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

TransRamHsR_addr- HDL params

PRIV_T - default value None of type None

ADDR_WIDTH - default value 32 of type int

USE_FLUSH - default value True of type bool

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

flush - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

hwtLib.mem.ramXor module¶

- class hwtLib.mem.ramXor.RamXorSingleClock(hdl_name_override: Optional[str] = None)[source]¶

Bases:

RamSingleClockMultiport XOR based RAM with only one clock signal

- HDL params

ADDR_WIDTH - default value 10 of type int

DATA_WIDTH - default value 64 of type int

PORT_CNT - default value (‘WRITE’, ‘WRITE’, ‘READ’) of type tuple

HAS_BE - default value False of type bool

MAX_BLOCK_DATA_WIDTH - default value None of type None

INIT_DATA - default value None of type None

PRIMITIVE_MEMORY_PORTS - default value (‘WRITE’, ‘READ’) of type tuple

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst - of type hwt.interfaces.std.Rst with dtype=<Bits, 1bit> - SLAVE

port_0 - of type hwt.interfaces.std.BramPort_withoutClk - SLAVE

port_1 - of type hwt.interfaces.std.BramPort_withoutClk - SLAVE

port_2 - of type hwt.interfaces.std.BramPort_withoutClk - SLAVE

- HDL components

w_rams_0_1 - of type hwtLib.mem.ram.RamSingleClock

w_rams_1_0 - of type hwtLib.mem.ram.RamSingleClock

r_rams_0_0 - of type hwtLib.mem.ram.RamSingleClock

r_rams_0_1 - of type hwtLib.mem.ram.RamSingleClock