hwtLib.amba.axi_comp.oooOp package¶

This package is dedicated to components and other utilities for out-of-order processing.

Submodules¶

hwtLib.amba.axi_comp.oooOp.outOfOrderCummulativeOp module¶

- class hwtLib.amba.axi_comp.oooOp.outOfOrderCummulativeOp.OutOfOrderCummulativeOp(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitOut of order container of read-modify-write cummulative operation.

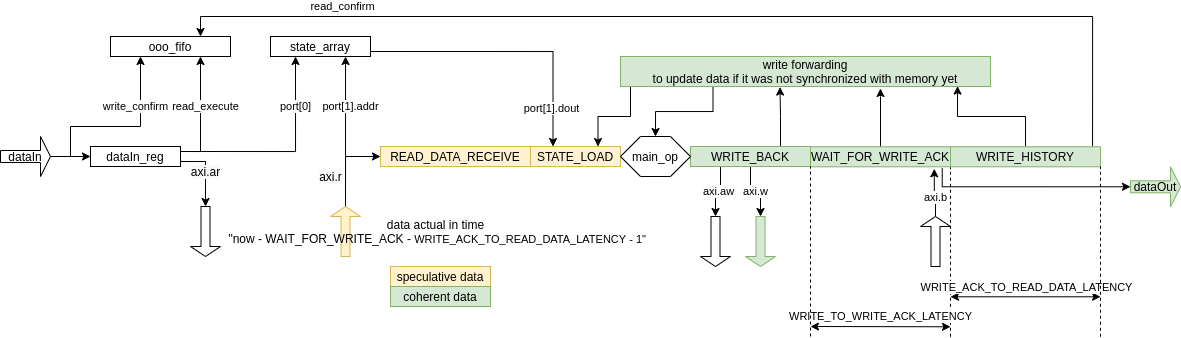

This is a component template for cumulative Out of Order operations with hihgh latency AXI. Suitable for counter arrays, hash tables and other data structures which are acessing data randomly and potential collision due read-modify-write operations may occure.

This component stores info about currently executed memory transactions which may be finished out of order. Potential memory access colisions are solved by write forwarding in main pipeline. In order to compensate for memory write latency the write history is utilised. The write history is a set of registers on the end of the pipeline.

Note that the write history is not meant as a main mechanism for write latency compensation. It is meant to be used for 3-4 items to componsate for latency of the cache/LSU.

If the main operation requires multiple clock cycles the operation is performed speculatively.

The most up-to-date version of the data is always selected on the input of WRITE_BACK stage.

The STATE_LOAD stage is meant for all write forwarding. The value in this stage is always updated to the latest version (with an exception of WRITE_BACK stage, explained later). The WRITE_BACK stage contains the data which is written to RAM. From this stage the value is confirmed. And the first data in pipeline from this stage is the latest version of it. Because we can not predict the value for WRITE_STAGE when updating STATE_LOAD we have to consider 2 possible values. The value in STATE_LOAD which holds latest value except for WRITE_BACK stage and the WRITE_BACK stage which holds the lates data for a latest transaction.

- Variables

MAIN_STATE_T – a type of the state in main memory which is being updated by this component

TRANSACTION_STATE_T – a type of the transaction state, used to store additional data for transaction and can be used to modify the behavior of the pipeline

- Note

If MAIN_STATE_T.bit_length() is smaller than DATA_WIDTH each item is allocated in a signle bus word separately in order to avoid alignment logic

- Note

provides axi aw and first w word in same clock cycle only

- apply_data_write_forwarding(st: ~hwtLib.amba.axi_comp.oooOp.utils.OOOOpPipelineStage, st_load_en: ~hwt.synthesizer.rtlLevel.rtlSignal.RtlSignal, data_modifier=<function OutOfOrderCummulativeOp.<lambda>>)[source]¶

- ar_dispatch()[source]¶

Send read request on AXI and store transaction in to state array and ooo_fifo for later wake up

- can_write_forward(src_st: OOOOpPipelineStage, dst_st: OOOOpPipelineStage)[source]¶

Used when collision detector is build. (for next value of st WRITE_BACK-1)

- collision_detector(pipeline: List[OOOOpPipelineStage]) List[List[RtlSignal]][source]¶

Search for address access collisions in pipeline and store the result of colision check to registers for data write forwarding in next clock cycle. The collision detector is build for STATE_LOAD (<P.WRITE_BACK) stages because we need to have collision information stored in registers in order to have enough time to do muxing in P.WRITE_BACK stage input.

- data_load(r: Axi4_r, st0: OOOOpPipelineStage)[source]¶

Receive all data words from a bus and store them into stage of the pipeline.

- data_store(st_data: Union[StructIntf, RtlSignal], w: Axi4_w, ack: RtlSignal)[source]¶

Transceive all data words from stage of pipeline to the bus.

- Parameters

ack – signal which is 1 if the data word is transfered on this write channel

- main_op(dst_st: OOOOpPipelineStage, src_st: OOOOpPipelineStage) RtlSignal[source]¶

Interpretation of main operatorion of the pipeline.

- propagate_trans_st(stage_from: OOOOpPipelineStage, stage_to: OOOOpPipelineStage)[source]¶

Propagate transaction state between two pipeline stages.

- write_cancel(st: OOOOpPipelineStage)[source]¶

- Returns

A signal/value which if it is 1 it means that the write back of this state should not be performed.

- write_forwarding_en(dst_st_load: RtlSignal, dst_st: OOOOpPipelineStage, dst_prev_st: OOOOpPipelineStage, src_st_i: int)[source]¶

hwtLib.amba.axi_comp.oooOp.reorder_buffer module¶

- class hwtLib.amba.axi_comp.oooOp.reorder_buffer.HsStructWithIdIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

HsStructIntf

- class hwtLib.amba.axi_comp.oooOp.reorder_buffer.HsStructWithIdIntfAgent(sim: HdlSimulator, intf: Handshaked, allowNoReset=False)[source]¶

Bases:

HandshakedAgent

- class hwtLib.amba.axi_comp.oooOp.reorder_buffer.ReorderBuffer(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitSerialize an unordered input sequence to continuous output sequence.

- HDL params

T - default value <Bits, 16bits, unsigned> of type hwt.hdl.types.bits.Bits

ID_WIDTH - default value 6 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

dataIn - of type hwtLib.amba.axi_comp.oooOp.reorder_buffer.HsStructWithIdIntf with dtype=<Bits, 16bits, unsigned> - SLAVE an input interface with an id signal which is used to reconstruct the sequence

dataOut - of type hwt.interfaces.hsStructIntf.HsStructIntf with dtype=<Bits, 16bits, unsigned> - MASTER an output interface with a data from dataIn which is ordered according to its id

- HDL components

storage_w - of type hwtLib.handshaked.ramAsHs.RamAsHs

storage_r - of type hwtLib.handshaked.ramAsHs.RamAsHs

storage_ram - of type hwtLib.mem.ram.RamSingleClock

gen_dataIn_reg_0 - of type hwtLib.handshaked.reg.HandshakedReg

- item_occupancy_reg() Tuple[RtlSignal, RtlSyncSignal, RtlSignal][source]¶

hwtLib.amba.axi_comp.oooOp.utils module¶

- class hwtLib.amba.axi_comp.oooOp.utils.OOOOpPipelineStage(index, name: str, parent: OutOfOrderCummulativeOp, has_transaction_state)[source]¶

Bases:

object- Variables

index – index of the register in pipeline

id – an id of an axi transaction (and index of item in state_array)

addr – an address which is beeing processed in this stage

state – state loaded from the state_array (current meta state)

data – currently loaded data from the bus

valid – validity flag for whole stage

ready – if 1 the stage can recieve data on next clock edge, otherwise the stage stalls

collision_detect – the list of flags (sotored in register) if flag is 1 it means that the value should be updated from stage on that index

load_en – if 1 the stage will load the data from previous stage in this clock cycle

- __init__(index, name: str, parent: OutOfOrderCummulativeOp, has_transaction_state)[source]¶

- class hwtLib.amba.axi_comp.oooOp.utils.OutOfOrderCummulativeOpIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

Handshaked- HDL params

TRANSACTION_STATE_T - default value <Bits, 8bits, unsigned> of type hwt.hdl.types.bits.Bits

MAIN_STATE_T - default value <Bits, 8bits, unsigned> of type hwt.hdl.types.bits.Bits

MAIN_STATE_INDEX_WIDTH - default value 8 of type int

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits, unsigned> - MASTER

transaction_state - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits, unsigned> - MASTER

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

- class hwtLib.amba.axi_comp.oooOp.utils.OutOfOrderCummulativeOpIntfAgent(sim: HdlSimulator, intf: OutOfOrderCummulativeOpIntf, allowNoReset=False)[source]¶

Bases:

HandshakedAgent- Note

if TRANSACTION_STATE_T is None the data should be only int for address else data should be tuple of int for address and a value of the state state value depends on state type, for simple bit vector it is just int, for struct it is tuple, …

- __init__(sim: HdlSimulator, intf: OutOfOrderCummulativeOpIntf, allowNoReset=False)[source]¶

- Parameters

rst – tuple (rst signal, rst_negated flag)

- class hwtLib.amba.axi_comp.oooOp.utils.OutOfOrderCummulativeOpPipelineConfig(READ_DATA_RECEIVE, STATE_LOAD, WRITE_BACK, WAIT_FOR_WRITE_ACK, WRITE_HISTORY_SIZE)[source]¶

Bases:

tuple- READ_DATA_RECEIVE: int¶

Alias for field number 0

- STATE_LOAD: int¶

Alias for field number 1

- WAIT_FOR_WRITE_ACK: int¶

Alias for field number 3

- WRITE_BACK: int¶

Alias for field number 2

- WRITE_HISTORY_SIZE: int¶

Alias for field number 4

- __annotations__ = {'READ_DATA_RECEIVE': <class 'int'>, 'STATE_LOAD': <class 'int'>, 'WAIT_FOR_WRITE_ACK': <class 'int'>, 'WRITE_BACK': <class 'int'>, 'WRITE_HISTORY_SIZE': <class 'int'>}¶

- __getnewargs__()¶

Return self as a plain tuple. Used by copy and pickle.

- static __new__(_cls, READ_DATA_RECEIVE: int, STATE_LOAD: int, WRITE_BACK: int, WAIT_FOR_WRITE_ACK: int, WRITE_HISTORY_SIZE: int)¶

Create new instance of OutOfOrderCummulativeOpPipelineConfig(READ_DATA_RECEIVE, STATE_LOAD, WRITE_BACK, WAIT_FOR_WRITE_ACK, WRITE_HISTORY_SIZE)

- __repr__()¶

Return a nicely formatted representation string

- __slots__ = ()¶

- _asdict()¶

Return a new dict which maps field names to their values.

- _field_defaults = {}¶

- _field_types = {'READ_DATA_RECEIVE': <class 'int'>, 'STATE_LOAD': <class 'int'>, 'WAIT_FOR_WRITE_ACK': <class 'int'>, 'WRITE_BACK': <class 'int'>, 'WRITE_HISTORY_SIZE': <class 'int'>}¶

- _fields = ('READ_DATA_RECEIVE', 'STATE_LOAD', 'WRITE_BACK', 'WAIT_FOR_WRITE_ACK', 'WRITE_HISTORY_SIZE')¶

- _fields_defaults = {}¶

- classmethod _make(iterable)¶

Make a new OutOfOrderCummulativeOpPipelineConfig object from a sequence or iterable

- _replace(**kwds)¶

Return a new OutOfOrderCummulativeOpPipelineConfig object replacing specified fields with new values