hwtLib.amba.axi_comp.lsu package¶

This package is dedicated to AXI Load/Store Units (LSU) a others like.

Other LSU implementations:

https://github.com/riscv-boom/riscv-boom - has RISC-V LSU in chisel3, read kill, MSHRs

https://github.com/rsd-devel/rsd - has N issue RISC-V LSU

https://github.com/bluespec/Toooba - has RISC-V LSU in BlueSpecVerilog

https://github.com/openhwgroup/cv32e40p - has RISC-V LSU for in order pipeline

Submodules¶

hwtLib.amba.axi_comp.lsu.fifo_oooread module¶

- class hwtLib.amba.axi_comp.lsu.fifo_oooread.FifoOutOfOrderRead(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitContainer of FIFO pointers and flags where the items can be discarded in out of order manner.

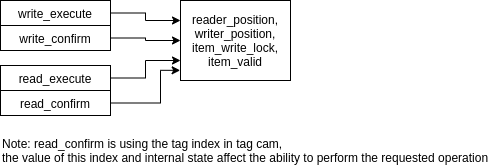

Item state control scheme:

write_confirm: the item is now allocated in the fifo and ready to be read

read_execute: the item is locked for updates and is currently being read

read_confirm: the item is entirely readed and it is ready to be deallocated

- HDL params

ITEMS - default value 4 of type int

KEY_WIDTH - default value 0 of type int

INIT_DATA - default value () of type tuple

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

write_confirm - of type hwt.interfaces.std.HandshakeSync - SLAVE

read_execute - of type hwtLib.common_nonstd_interfaces.index_key_hs.IndexKeyHs - MASTER

read_confirm - of type hwt.interfaces.std.Handshaked - SLAVE

- class hwtLib.amba.axi_comp.lsu.fifo_oooread.FifoOutOfOrderReadFiltered(hdl_name_override: Optional[str] = None)[source]¶

Bases:

FifoOutOfOrderReadFifoOutOfOrderReadwith an additional cam to filter transactions by same key :attention: this component does not contains the item storage, it is just container of such a FIFO logic

Item state control scheme:

write_execute: preallocate the item for writing (and add key to CAM for filtering)

write_confirm: the item is now allocated in the fifo and ready to be read

read_execute: the item is locked for updates and is currently being read

read_confirm: the item is entirely readed and it is ready to be deallocated

- HDL params

ITEMS - default value 4 of type int

KEY_WIDTH - default value 8 of type int

INIT_DATA - default value () of type tuple

HAS_READ_LOOKUP - default value False of type bool

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

write_confirm - of type hwt.interfaces.std.HandshakeSync - SLAVE

read_execute - of type hwtLib.common_nonstd_interfaces.index_key_hs.IndexKeyHs - MASTER

read_confirm - of type hwt.interfaces.std.Handshaked - SLAVE

write_pre_lookup - of type hwt.interfaces.std.Handshaked - SLAVE

write_pre_lookup_res - of type hwt.interfaces.std.Handshaked - MASTER

item_valid - of type hwt.interfaces.std.Signal with dtype=<Bits, 4bits> - MASTER

item_write_lock - of type hwt.interfaces.std.Signal with dtype=<Bits, 4bits> - MASTER

write_execute - of type hwtLib.common_nonstd_interfaces.index_key_hs.IndexKeyInHs - MASTER

- HDL components

tag_cam - of type hwtLib.amba.axi_comp.cache.utils.CamWithReadPort

hwtLib.amba.axi_comp.lsu.interfaces module¶

- class hwtLib.amba.axi_comp.lsu.interfaces.AddrDataIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

Interface- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 64bits> - SLAVE (Master=IN)

- class hwtLib.amba.axi_comp.lsu.interfaces.AxiWriteAggregatorReadIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

InterfaceAn interface which is used to speculatively read data from AxiWriteAggregator

- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

- HDL IO

a - of type hwtLib.amba.axi3Lite.Axi3Lite_addr - MASTER

r_data_available - of type hwt.interfaces.std.Handshaked - MASTER

r - of type hwtLib.amba.axi3Lite.Axi3Lite_r - MASTER

- class hwtLib.amba.axi_comp.lsu.interfaces.AxiWriteAggregatorWriteTmpIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

AxiStreamInterface for tmp input register on store buffer write input

- HDL params

IS_BIGENDIAN - default value False of type bool

USE_STRB - default value True of type bool

USE_KEEP - default value False of type bool

ID_WIDTH - default value 0 of type int

DEST_WIDTH - default value 0 of type int

DATA_WIDTH - default value 64 of type int

USER_WIDTH - default value 0 of type int

ADDR_WIDTH - default value 32 of type int

ITEMS - default value 64 of type int

- HDL IO

addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 32bits> - MASTER

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 64bits> - MASTER

strb - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

last - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

ready - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

valid - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

colides_with_last_addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

cam_lookup - of type hwt.interfaces.std.Signal with dtype=<Bits, 64bits> - MASTER VectSignal with value of lookup from item cam (1 if cacheline present in store buffer)

mask_byte_unaligned - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER Signal 1 if any byte of mask is 0 or all 1

hwtLib.amba.axi_comp.lsu.read_aggregator module¶

- class hwtLib.amba.axi_comp.lsu.read_aggregator.AxiReadAggregator(hdl_name_override: Optional[str] = None)[source]¶

Bases:

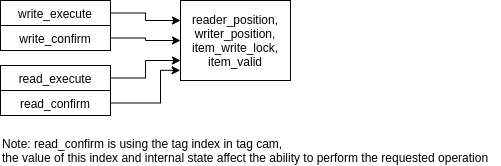

UnitThis is a component which reduces reads from same address.

This component has several slots for read transactions, Each slot has it’s own address record in CAM which is used to detect reads from same address, if the read is from same address which is currently being loaded. The read thread is put to sleep until data for previous read is received. After data is received it is copied as a response also for this transaction.

- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

ID_WIDTH - default value 2 of type int

ADDR_USER_WIDTH - default value 0 of type int

CACHE_LINE_SIZE - default value 64 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

s - of type hwtLib.amba.axi4.Axi4 - SLAVE

m - of type hwtLib.amba.axi4.Axi4 - MASTER

- HDL components

frame_buff - of type hwtLib.amba.axis_comp.fifoCopy.AxiSFifoCopy

addr_cam - of type hwtLib.mem.cam.CamMultiPort

addr_cam_out_reg - of type hwtLib.handshaked.reg.HandshakedReg

s_ar_tmp - of type hwtLib.amba.axis_comp.reg.AxiSReg

hwtLib.amba.axi_comp.lsu.store_queue_write_propagating module¶

- class hwtLib.amba.axi_comp.lsu.store_queue_write_propagating.AxiStoreQueueWritePropagating(hdl_name_override: Optional[str] = None)[source]¶

Bases:

AxiWriteAggregatorAn extension of

hwtLib.amba.axi_comp.lsu.write_aggregator.AxiWriteAggregatorwith an IO for a communication with anhwtLib.amba.axi_comp.lsu.load_queue.AxiLoadQueueDoes the same thing and allowshwtLib.amba.axi_comp.lsu.load_queue_write_propagating.AxiLoadQueueWritePropagatingto speculatively read the data and listen for write transactions. The component allows for write to bypass read, which makes it suitable for cumulative operations, but more complicated for a generic use.- Variables

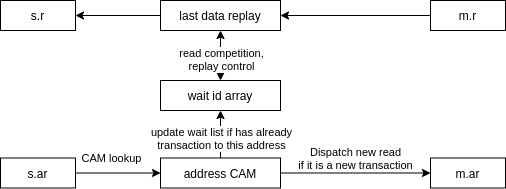

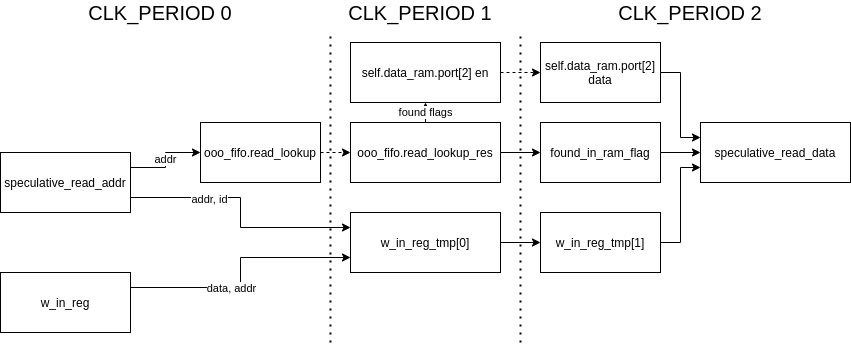

speculative_read_addr – port used for load buffer to speculatively read the data from this component. If data is not present the speculative_read_data returns RESP_EXOKAY error. The data may also be flushed during the read this is marked with RESP_SLVERR error.

speculative_read_data – Read data for speculative read.

- speculative_read_handler()[source]¶

Connect the speculative_read port to internal storages of the

AxiWriteAggregatorWe need to handle several cases:

the data is currently stuck in tmp register (we need to wait)

the data was in tmp register and now is in data_ram

the data was and is in data_ram

the data was in data_ram and now it is in main memory

the data was not found in this component (is in main memory)

Handling of speculative read has following stages:

search input register and main address CAM for data

optionaly load the data from ram

send data to speculative_read_data and set resp to error if was not found it may also happen that the data was flushed in the mean time we can not blok other channel and we need to have a buffer for 1 transaction to prevent data loose where we would need to ask main memory

- Note

speculative read never block the write channel and thus data may be invalid if the speculative read data is stalled. This should be handled in master of speculative read port (Other component which is using this component).

- class hwtLib.amba.axi_comp.lsu.store_queue_write_propagating.AxiWriteAggregatorWriteTmpIntf(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

Handshaked

hwtLib.amba.axi_comp.lsu.write_aggregator module¶

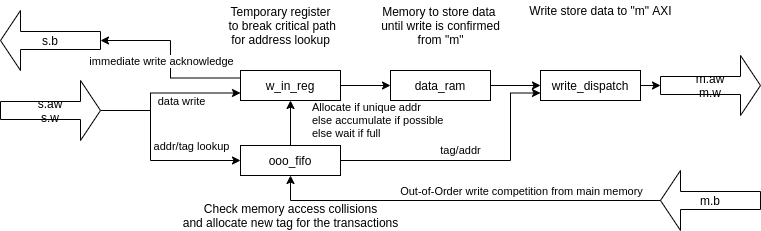

- class hwtLib.amba.axi_comp.lsu.write_aggregator.AxiWriteAggregator(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitA buffer which is used for write data from cache.

It manages:

out of order write acknowledge

write transaction merging

- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 32 of type int

ID_WIDTH - default value 2 of type inta parameter which specifies width of axi id signal, it also specifies the number of items in this buffer (2**ID_WIDTH)

CACHE_LINE_SIZE - default value 4 of type int

MAX_BLOCK_DATA_WIDTH - default value 8 of type intspecifies maximum data width of RAM (used to prevent synthesis problems for tools which can not handle too wide memories with byte enable)

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

s - of type hwtLib.amba.axi4.Axi4 - SLAVE

m - of type hwtLib.amba.axi4.Axi4 - MASTER

- HDL components

write_dispatch - of type hwtLib.amba.axi_comp.lsu.write_aggregator_write_dispatcher.AxiWriteAggregatorWriteDispatcher

ooo_fifo - of type hwtLib.amba.axi_comp.lsu.fifo_oooread.FifoOutOfOrderReadFiltered

data_ram - of type hwtLib.mem.ramCumulativeMask.RamCumulativeMask

gen_b_reg_0 - of type hwtLib.amba.axis_comp.reg.AxiSReg

w_in_reg - of type hwtLib.amba.axis_comp.reg.AxiSReg

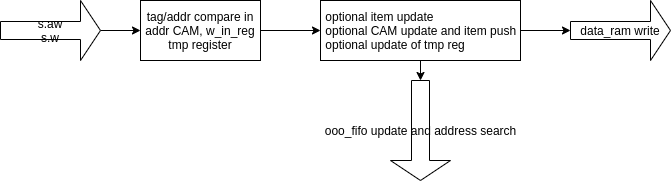

- data_insert(items: BramPort_withReadMask_withoutClk)[source]¶

if it is possible to update data in data_ram of this buffer

else allocate new data (insert to address CAM of ooo_fifo) and store data to w_in_reg

- resolve_cam_index(w_tmp_out: AxiWriteAggregatorWriteTmpIntf)[source]¶

- w_in_tmp_reg_load() AxiWriteAggregatorWriteTmpIntf[source]¶

check if this address is already present in address CAM or w_in_reg

hwtLib.amba.axi_comp.lsu.write_aggregator_write_dispatcher module¶

- class hwtLib.amba.axi_comp.lsu.write_aggregator_write_dispatcher.AxiWriteAggregatorWriteDispatcher(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitUse

hwtLib.amba.axi_comp.lsu.fifo_oooread.FifoOutOfOrderReadFilteredread ports to query an AXI transaction info and copy paste this transaction from BRAM to AXI.- HDL params

ADDR_WIDTH - default value 32 of type int

DATA_WIDTH - default value 64 of type int

ID_WIDTH - default value 6 of type int

CACHE_LINE_SIZE - default value 64 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

data - of type hwtLib.mem.ramCumulativeMask.BramPort_withReadMask_withoutClk - MASTER

read_execute - of type hwtLib.common_nonstd_interfaces.index_key_hs.IndexKeyHs - SLAVE

read_confirm - of type hwt.interfaces.std.Handshaked - MASTER

m - of type hwtLib.amba.axi4.Axi4 - MASTER

- data_ram_read_to_bus_w(items: BramPort_withReadMask_withoutClk, item_last: RtlSignal, w_out: Axi4_w)[source]¶

Read write data from data_ram

- Parameters

item_last – the signal with last flag for data (notes a last beat in burst) sampled in the same time as an read address

- dispatch_addr(id_to_use: RtlSignal, addr: RtlSignal, a: Axi4_addr)[source]¶

if there is a valid item in buffer dispatch read request

- dispatch_data(aw_ld: RtlSignal, pop_ptr: RtlSignal, pop_req: RtlSignal, pop_wait: RtlSignal, items: BramPort_withReadMask_withoutClk, aw_out_ready: RtlSignal, w_out: Axi4_w)[source]¶

if there is a valid item in buffer dispatch write request and write data

handshaked FIFO read logic

- receive_write_confirm(b: Axi4_b, read_confirm: Handshaked)[source]¶