hwtLib.peripheral.usb.usb2 package¶

Submodules¶

hwtLib.peripheral.usb.usb2.device_cdc_vcp module¶

- class hwtLib.peripheral.usb.usb2.device_cdc_vcp.Usb2CdcVcp(hdl_name_override: Optional[str] = None)[source]¶

Bases:

Usb2DeviceCommonUSB2.0 communcation device class virtual com port core (serial/uart over USB)

- HDL params

DESCRIPTORS - default value [{ header: { bLength: <BitsVal 18> bDescriptorType: <BitsVal 1> } body: { bcdUSB: <BitsVal 512> bDeviceClass: <BitsVal 2> bDeviceSubClass: <BitsVal 0> bDeviceProtocol: <BitsVal 0> bMaxPacketSize: <BitsVal 64> idVendor: <BitsVal 0> idProduct: <BitsVal 0> bcdDevice: <BitsVal 0> iManufacturer: <BitsVal 0> iProduct: <BitsVal 1> iSerialNumber: <BitsVal 0> bNumConfigurations: <BitsVal 1> } }, { header: { bLength: <BitsVal 9> bDescriptorType: <BitsVal 2> } body: { wTotalLength: <BitsVal 67> bNumInterfaces: <BitsVal 2> bConfigurationValue: <BitsVal 1> iConfiguration: <BitsVal 0> bmAttributes: { reserved0: <BitsVal 0> remoteWakeup: <BitsVal 0> selfPowered: <BitsVal 0> reserved1: <BitsVal 1> } bMaxPower: <BitsVal 250> } }, { header: { bLength: <BitsVal 9> bDescriptorType: <BitsVal 4> } body: { bInterfaceNumber: <BitsVal 0> bAlternateSetting: <BitsVal 0> bNumEndpoints: <BitsVal 1> bInterfaceClass: <BitsVal 2> bInterfaceSubClass: <BitsVal 2> bInterfaceProtocol: <BitsVal 1> iInterface: <BitsVal 0> } }, { header: { bLength: <BitsVal 5> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 0> } body: { bcdCDC: <BitsVal 272> } }, { header: { bLength: <BitsVal 5> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 1> } body: { bmCapabilities: { supportHandlesCallManagementItself: <BitsVal 0> supportManagementOverDataClassInterface: <BitsVal 0> reserved0: <BitsVal 0> } bDataInterface: <BitsVal 1> } }, { header: { bLength: <BitsVal 4> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 2> } body: { bmCapabilities: { commFeature: <BitsVal 0> lineCodingAndSerialState: <BitsVal 0> sendBreak: <BitsVal 0> networkConnection: <BitsVal 0> reserved0: <BitsVal 0> } } }, { header: { bLength: <BitsVal 5> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 6> } body: { bMasterInterface: <BitsVal 0> bSlaveInterface: <HArrayVal {0: <BitsVal 1>}> } }, { header: { bLength: <BitsVal 7> bDescriptorType: <BitsVal 5> } body: { bEndpointAddress: <BitsVal 2> bEndpointAddressDir: <BitsVal 1> bmAttributes: { transferType: <BitsVal 3> synchronisationType: <BitsVal 0> usageType: <BitsVal 0> reserved0: <BitsVal 0> } wMaxPacketSize: <BitsVal 8> bInterval: <BitsVal 10> } }, { header: { bLength: <BitsVal 9> bDescriptorType: <BitsVal 4> } body: { bInterfaceNumber: <BitsVal 1> bAlternateSetting: <BitsVal 0> bNumEndpoints: <BitsVal 2> bInterfaceClass: <BitsVal 10> bInterfaceSubClass: <BitsVal 0> bInterfaceProtocol: <BitsVal 0> iInterface: <BitsVal 0> } }, { header: { bLength: <BitsVal 7> bDescriptorType: <BitsVal 5> } body: { bEndpointAddress: <BitsVal 1> bEndpointAddressDir: <BitsVal 0> bmAttributes: { transferType: <BitsVal 2> synchronisationType: <BitsVal 0> usageType: <BitsVal 0> reserved0: <BitsVal 0> } wMaxPacketSize: <BitsVal 512> bInterval: <BitsVal 0> } }, { header: { bLength: <BitsVal 7> bDescriptorType: <BitsVal 5> } body: { bEndpointAddress: <BitsVal 1> bEndpointAddressDir: <BitsVal 1> bmAttributes: { transferType: <BitsVal 2> synchronisationType: <BitsVal 0> usageType: <BitsVal 0> reserved0: <BitsVal 0> } wMaxPacketSize: <BitsVal 512> bInterval: <BitsVal 0> } }, { header: { bLength: <BitsVal 4> bDescriptorType: <BitsVal 3> } body: <HArrayVal {0: <BitsVal 1033>}> }, { header: { bLength: <BitsVal 24> bDescriptorType: <BitsVal 3> } body: <HArrayVal {0: <BitsVal 255>, 1: <BitsVal 254>, 2: <BitsVal 85>, 3: <BitsVal 0>, 4: <BitsVal 115>, 5: <BitsVal 0>, 6: <BitsVal 98>, 7: <BitsVal 0>, 8: <BitsVal 50>, 9: <BitsVal 0>, 10: <BitsVal 67>, 11: <BitsVal 0>, 12: <BitsVal 100>, 13: <BitsVal 0>, 14: <BitsVal 99>, 15: <BitsVal 0>, 16: <BitsVal 86>, 17: <BitsVal 0>, 18: <BitsVal 99>, 19: <BitsVal 0>, 20: <BitsVal 112>, 21: <BitsVal 0>}> }] of type hwtLib.peripheral.usb.descriptors.bundle.UsbDescriptorBundle

CLK_FREQ - default value 60000000 of type int

PRE_NEGOTIATED_TO - default value None of type None

RX_AGGREGATION_TIMEOUT - default value 512 of type intthe timeout (in clk ticks) for a packing of incomming bytes to a USB packet (the bigger packet equals more USB efficiency)

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

phy - of type hwtLib.peripheral.usb.usb2.utmi.Utmi_8b - SLAVE

usb_rst - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rx - of type hwt.interfaces.std.Handshaked - MASTER stream data from host

tx - of type hwt.interfaces.std.Handshaked - SLAVE stream data to host

- HDL components

usb_core - of type hwtLib.peripheral.usb.usb2.device_core.Usb2DeviceCore

ep_buffers - of type hwtLib.peripheral.usb.usb2.device_ep_buffers.UsbDeviceEpBuffers

gen_tx_hsToAxiS_0 - of type hwtLib.handshaked.handshakedToAxiStream.HandshakedToAxiStream

- decode_setup_request_class(setup: StructIntf, ep0_stall: RtlSignal, usb_addr_next: RtlSignal, descriptors: UsbDescriptorBundle, req_bDescriptorType: RtlSignal, req_bDescriptorIndex: RtlSignal, dev_configured: RtlSignal, descr_addr: RtlSignal, ep0_trans_len: RtlSignal)[source]¶

- generat_descriptor_rom(descriptors: UsbDescriptorBundle, rst)[source]¶

hwtLib.peripheral.usb.usb2.device_common module¶

- class hwtLib.peripheral.usb.usb2.device_common.Usb2DeviceCommon(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitUSB2.0 device common parts. This component directly handles the functionality of the EP0 and connects the usb_core to ep_buffers.

- Attention

This is an abstract class, which holds the functionality shared between usb devices. In order to use it it needs to be extended to some specific usb device.

- Variables

usb_core – Handles the USB protocol reset, ping, SOF and handshake messages

ep_buffers – handles the data multiplexing and replaying on errors,

- connect_core_and_ep_buffers_common(ep0_stall, ep_buffers: UsbDeviceEpBuffers)[source]¶

- decode_setup_request(setup: StructIntf, ep0_stall: RtlSignal, usb_addr_next: RtlSignal, descriptors: UsbDescriptorBundle, req_bDescriptorType: RtlSignal, req_bDescriptorIndex: RtlSignal, dev_configured: RtlSignal, descr_addr: RtlSignal, ep0_trans_len: RtlSignal)[source]¶

- decode_setup_request_class(setup: StructIntf, ep0_stall: RtlSignal, usb_addr_next: RtlSignal, descriptors: UsbDescriptorBundle, req_bDescriptorType: RtlSignal, req_bDescriptorIndex: RtlSignal, dev_configured: RtlSignal, descr_addr: RtlSignal, ep0_trans_len: RtlSignal)[source]¶

- descriptor_ep0_fsm(descriptors: UsbDescriptorBundle)[source]¶

The Control enpoint (EP0) functionality

- descriptor_ep0_fsm_get_descriptor(descr_bundle: UsbDescriptorBundle, setup_wLength: RtlSignal, req_bDescriptorType: RtlSignal, req_bDescriptorIndex: RtlSignal, descr_addr: RtlSignal, ep0_get_len: RtlSignal, ep0_stall: RtlSignal)[source]¶

Get descriptor part of the FSM for EP0 configuration endpoint

- Parameters

req_bDescriptorType – the bDescriptorType from the usb device request

req_bDescriptorIndex – the bDescriptorIndex from the usb device request

descr_addr – read address for current descriptor read

ep0_get_len – size how many descriptor bytes should be read

- generat_descriptor_rom(descriptors: UsbDescriptorBundle, rst)[source]¶

hwtLib.peripheral.usb.usb2.device_core module¶

- class hwtLib.peripheral.usb.usb2.device_core.Usb2DeviceCore(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitBased on USB descriptors build endpoint statemachines, speed negotiation logic, usb reset logic and transaction logic

- Variables

~.phy – An interface to USB PHY which is connected to host

~.ep – And interface to USB endpont buffers of this device

~.usb_rst – output of USB reset detector

~.usb_speed – An interface which holds the index of the USB version to note which speed was negotiated.

~.current_usb_addr – An input signal with an address currently assigned for this device.

~.PRE_NEGOTIATED_TO – A parameter for testing purposes which can be used to specify the default state of the link negotiation state

- HDL params

DESCRIPTORS - default value [{ header: { bLength: <BitsVal 18> bDescriptorType: <BitsVal 1> } body: { bcdUSB: <BitsVal 512> bDeviceClass: <BitsVal 2> bDeviceSubClass: <BitsVal 0> bDeviceProtocol: <BitsVal 0> bMaxPacketSize: <BitsVal 64> idVendor: <BitsVal 0> idProduct: <BitsVal 0> bcdDevice: <BitsVal 0> iManufacturer: <BitsVal 0> iProduct: <BitsVal 0> iSerialNumber: <BitsVal 0> bNumConfigurations: <BitsVal 1> } }, { header: { bLength: <BitsVal 9> bDescriptorType: <BitsVal 2> } body: { wTotalLength: <BitsVal 67> bNumInterfaces: <BitsVal 2> bConfigurationValue: <BitsVal 1> iConfiguration: <BitsVal 0> bmAttributes: { reserved0: <BitsVal 0> remoteWakeup: <BitsVal 0> selfPowered: <BitsVal 0> reserved1: <BitsVal 1> } bMaxPower: <BitsVal 250> } }, { header: { bLength: <BitsVal 9> bDescriptorType: <BitsVal 4> } body: { bInterfaceNumber: <BitsVal 0> bAlternateSetting: <BitsVal 0> bNumEndpoints: <BitsVal 1> bInterfaceClass: <BitsVal 2> bInterfaceSubClass: <BitsVal 2> bInterfaceProtocol: <BitsVal 1> iInterface: <BitsVal 0> } }, { header: { bLength: <BitsVal 5> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 0> } body: { bcdCDC: <BitsVal 272> } }, { header: { bLength: <BitsVal 5> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 1> } body: { bmCapabilities: { supportHandlesCallManagementItself: <BitsVal 0> supportManagementOverDataClassInterface: <BitsVal 0> reserved0: <BitsVal 0> } bDataInterface: <BitsVal 1> } }, { header: { bLength: <BitsVal 4> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 2> } body: { bmCapabilities: { commFeature: <BitsVal 0> lineCodingAndSerialState: <BitsVal 0> sendBreak: <BitsVal 0> networkConnection: <BitsVal 0> reserved0: <BitsVal 0> } } }, { header: { bLength: <BitsVal 5> bDescriptorType: <BitsVal 36> bDescriptorSubtype: <BitsVal 6> } body: { bMasterInterface: <BitsVal 0> bSlaveInterface: <HArrayVal {0: <BitsVal 1>}> } }, { header: { bLength: <BitsVal 7> bDescriptorType: <BitsVal 5> } body: { bEndpointAddress: <BitsVal 2> bEndpointAddressDir: <BitsVal 1> bmAttributes: { transferType: <BitsVal 3> synchronisationType: <BitsVal 0> usageType: <BitsVal 0> reserved0: <BitsVal 0> } wMaxPacketSize: <BitsVal 8> bInterval: <BitsVal 10> } }, { header: { bLength: <BitsVal 9> bDescriptorType: <BitsVal 4> } body: { bInterfaceNumber: <BitsVal 1> bAlternateSetting: <BitsVal 0> bNumEndpoints: <BitsVal 2> bInterfaceClass: <BitsVal 10> bInterfaceSubClass: <BitsVal 0> bInterfaceProtocol: <BitsVal 0> iInterface: <BitsVal 0> } }, { header: { bLength: <BitsVal 7> bDescriptorType: <BitsVal 5> } body: { bEndpointAddress: <BitsVal 1> bEndpointAddressDir: <BitsVal 0> bmAttributes: { transferType: <BitsVal 2> synchronisationType: <BitsVal 0> usageType: <BitsVal 0> reserved0: <BitsVal 0> } wMaxPacketSize: <BitsVal 64> bInterval: <BitsVal 0> } }, { header: { bLength: <BitsVal 7> bDescriptorType: <BitsVal 5> } body: { bEndpointAddress: <BitsVal 1> bEndpointAddressDir: <BitsVal 1> bmAttributes: { transferType: <BitsVal 2> synchronisationType: <BitsVal 0> usageType: <BitsVal 0> reserved0: <BitsVal 0> } wMaxPacketSize: <BitsVal 64> bInterval: <BitsVal 0> } }, { header: { bLength: <BitsVal 4> bDescriptorType: <BitsVal 3> } body: <HArrayVal {0: <BitsVal 1033>}> }] of type hwtLib.peripheral.usb.descriptors.bundle.UsbDescriptorBundle

CLK_FREQ - default value 60000000 of type int

PRE_NEGOTIATED_TO - default value None of type None

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

phy - of type hwtLib.peripheral.usb.usb2.utmi.Utmi_8b - SLAVE

ep - of type hwtLib.peripheral.usb.usb2.device_core_interfaces.UsbEndpointInterface - MASTER

usb_rst - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

usb_speed - of type hwt.interfaces.std.VldSynced - MASTER

current_usb_addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 7bits> - SLAVE

- HDL components

sie_rx - of type hwtLib.peripheral.usb.usb2.sie_rx.Usb2SieDeviceRxSerial Interface Engine for UTMI rx channel (host->device)

sie_tx - of type hwtLib.peripheral.usb.usb2.sie_tx.Usb2SieDeviceTxSerial Interface Engine for UTMI tx channel (device->host)

hwtLib.peripheral.usb.usb2.device_core_interfaces module¶

- class hwtLib.peripheral.usb.usb2.device_core_interfaces.UsbEndpointInterface(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

InterfaceAn interface to transfer data between the USB core and endpont memory/usb function

- Variables

ep – endpoint number

stall – 1 if endpoint is dissabled or request is not supported

- HDL params

HAS_RX - default value True of type bool

HAS_TX - default value True of type bool

DATA_WIDTH - default value 8 of type int

- HDL IO

endp - of type hwt.interfaces.std.VldSynced - MASTER

rx_stall - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

rx - of type hwtLib.amba.axis.AxiStream - MASTER data from host to device(function)

tx_stall - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

tx - of type hwtLib.amba.axis.AxiStream - SLAVE (Master=IN) data from device(function) to host

tx_success - of type hwt.interfaces.std.VldSynced - MASTER tells the endpoint buffer that previously send packet was successfully transfered and the packet can be deallocated (if tx_sucess.vld & ~tx_sucess.data it means that the packet needs to be retransmited)

hwtLib.peripheral.usb.usb2.device_ep_buffers module¶

- class hwtLib.peripheral.usb.usb2.device_ep_buffers.UsbDeviceEpBuffers(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitUSB device endpoint buffers Buffers for the data transfers which are between usb core and usb function.

- HDL params

ENDPOINT_META - default value ([<UsbEndpointMeta EP0 OUT [‘setup’] maxPacketSize:64B>, <UsbEndpointMeta EP0 IN [‘setup’] maxPacketSize:64B>], [<UsbEndpointMeta EP1 OUT [‘setup’] maxPacketSize:64B>, <UsbEndpointMeta EP1 IN [‘setup’] maxPacketSize:64B>], [None, <UsbEndpointMeta EP2 IN [‘setup’] maxPacketSize:8B>]) of type tuple

DATA_WIDTH - default value 8 of type int

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

usb_core_io - of type hwtLib.peripheral.usb.usb2.device_core_interfaces.UsbEndpointInterface - SLAVE

ep_0 - of type hwtLib.amba.axis_fullduplex.AxiStreamFullDuplex - SLAVE

ep_1 - of type hwtLib.amba.axis_fullduplex.AxiStreamFullDuplex - SLAVE

ep_2 - of type hwtLib.amba.axis_fullduplex.AxiStreamFullDuplex - SLAVE

- HDL components

rx_fifos_1 - of type hwtLib.amba.axis_comp.fifoDrop.AxiSFifoDrop

tx_fifos_1 - of type hwtLib.amba.axis_comp.fifoCopy.AxiSFifoCopy

tx_fifos_2 - of type hwtLib.amba.axis_comp.fifoCopy.AxiSFifoCopy

tx_packet_buffered_fifos_1 - of type hwtLib.handshaked.fifo.HandshakedFifo

tx_packet_buffered_fifos_2 - of type hwtLib.handshaked.fifo.HandshakedFifo

- connect_rx_part(rx_channels: List[Tuple[int, AxiStream, UsbEndpointMeta, AxiSFifoDrop]])[source]¶

- connect_tx_part(tx_channels: List[Tuple[int, AxiStream, UsbEndpointMeta, AxiSFifoCopy, HandshakedFifo]])[source]¶

hwtLib.peripheral.usb.usb2.sie_interfaces module¶

- class hwtLib.peripheral.usb.usb2.sie_interfaces.DataErrVldKeepLast(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

VldSynced- HDL params

DATA_WIDTH - default value 64 of type int

USE_KEEP - default value True of type bool

- HDL IO

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 64bits> - MASTER

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

keep - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

error - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

last - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

- class hwtLib.peripheral.usb.usb2.sie_interfaces.DataErrVldKeepLastAgent(sim: HdlSimulator, intf, allowNoReset=False)[source]¶

Bases:

VldSyncedAgentA simulation agent for

DataErrVldKeepLastinterface.

- class hwtLib.peripheral.usb.usb2.sie_interfaces.Usb2SieRxOut(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

VldSynced- HDL IO

pid - of type hwt.interfaces.std.Signal with dtype=<Bits, 4bits> - MASTER

endp - of type hwt.interfaces.std.Signal with dtype=<Bits, 4bits> - MASTER

frame_number - of type hwt.interfaces.std.Signal with dtype=<Bits, 11bits> - MASTER

error - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

- class hwtLib.peripheral.usb.usb2.sie_interfaces.Usb2SieRxOutAgent(sim: HdlSimulator, intf, allowNoReset=False)[source]¶

Bases:

VldSyncedAgentA simulation agent for

Usb2SieRxOutinterface.

hwtLib.peripheral.usb.usb2.sie_rx module¶

- class hwtLib.peripheral.usb.usb2.sie_rx.Usb2SieDeviceRx(hdl_name_override: Optional[str] = None)[source]¶

Bases:

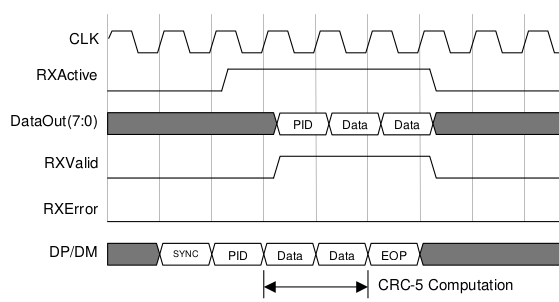

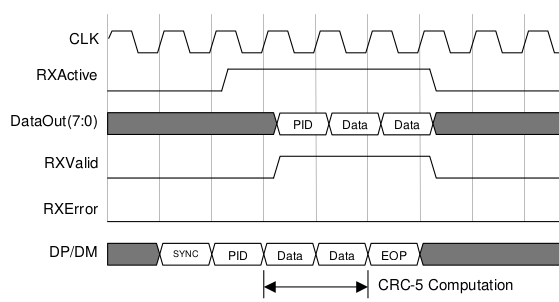

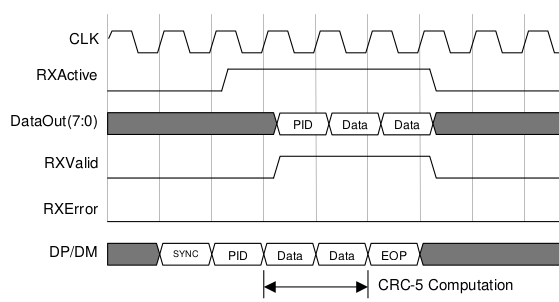

UnitUTMI rx (host->device) packet parser and CRC checker and cutter, (SIE stands for serial interface engine)

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

enable - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE

rx - of type hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_rx - SLAVE

current_usb_addr - of type hwt.interfaces.std.Signal with dtype=<Bits, 7bits> - SLAVE

rx_header - of type hwtLib.peripheral.usb.usb2.sie_interfaces.Usb2SieRxOut - MASTER

rx_data - of type hwtLib.peripheral.usb.usb2.sie_interfaces.DataErrVldKeepLast - MASTER

- HDL components

parser_pid - of type hwtLib.amba.axis_comp.frame_parser._parser.AxiS_frameParser

parser_token - of type hwtLib.amba.axis_comp.frame_parser._parser.AxiS_frameParser

parser_payload - of type hwtLib.amba.axis_comp.frame_parser._parser.AxiS_frameParser

crc5 - of type hwtLib.logic.crcComb.CrcComb

crc16 - of type hwtLib.logic.crc.Crc

gen_payload_reg_0 - of type hwtLib.amba.axis_comp.reg.AxiSReg

- _Utmi_8b_rx_to_DataErrVldStrbLast(rx: Utmi_8b_rx)[source]¶

hwtLib.peripheral.usb.usb2.sie_tx module¶

- class hwtLib.peripheral.usb.usb2.sie_tx.Usb2SieDeviceTx(hdl_name_override: Optional[str] = None)[source]¶

Bases:

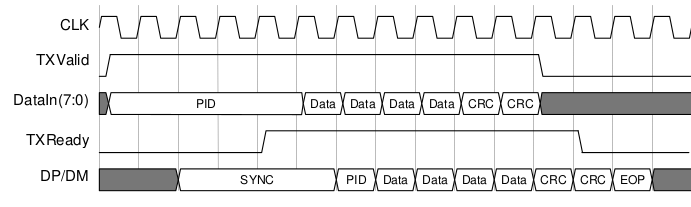

UnitUTMI Tx packet CRC appender and chirp inserter, (SIE stands for serial interface engine)

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst_n - of type hwt.interfaces.std.Rst_n with dtype=<Bits, 1bit> - SLAVE

enable - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE

tx_cmd - of type hwtLib.peripheral.usb.usb2.sie_tx.Usb2SieDeviceTxInput - SLAVE An interface which should be used to control this component

tx - of type hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_tx - MASTER The Tx part of the Utmi_8b interface

- HDL components

deparser_hs - of type hwtLib.amba.axis_comp.frame_deparser._deparser.AxiS_frameDeparser

deparser_data - of type hwtLib.amba.axis_comp.frame_deparser._deparser.AxiS_frameDeparser

gen_tx_cmd_reg_0 - of type hwtLib.amba.axis_comp.reg.AxiSReg

crc16 - of type hwtLib.logic.crc.Crc

gen_join_gen_join_join_0 - of type hwtLib.amba.axis_comp.joinPrioritized.AxiSJoinPrioritized

- _AxiStream_to_Utmi_8b_tx(axis: AxiStream, tx: Utmi_8b_tx)[source]¶

Convert last signal to a space between packets

- class hwtLib.peripheral.usb.usb2.sie_tx.Usb2SieDeviceTxInput(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

AxiStream- HDL params

IS_BIGENDIAN - default value False of type bool

USE_STRB - default value False of type bool

USE_KEEP - default value True of type bool

ID_WIDTH - default value 0 of type int

DEST_WIDTH - default value 0 of type int

DATA_WIDTH - default value 8 of type int

USER_WIDTH - default value 0 of type int

- HDL IO

pid - of type hwt.interfaces.std.Signal with dtype=<Bits, 4bits> - MASTER

chirp - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

keep - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit, force_vector> - MASTER

last - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

ready - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

valid - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

hwtLib.peripheral.usb.usb2.ulpi module¶

- class hwtLib.peripheral.usb.usb2.ulpi.IP_Ulpi[source]¶

Bases:

IntfIpMeta- library¶

- name¶

- vendor¶

- version¶

- class hwtLib.peripheral.usb.usb2.ulpi.ULPI_REG[source]¶

Bases:

object- Note

all registers are 8b in size

- Carkit_Control = 25¶

- Carkit_Interrupt_Delay = 28¶

- Carkit_Interrupt_Enable = 29¶

- Carkit_Interrupt_Latch = 33¶

- Carkit_Interrupt_Status = 32¶

- Carkit_Pulse_Control = 34¶

- Debug = 21¶

- Function_Control = 4¶

- Interface_Control = 7¶

- OTG_Control = 10¶

- Product_ID_High = 3¶

- Product_ID_Low = 2¶

- REGS_WITH_SET_AND_CLR = [4, 7, 10, 13, 16, 22, 25, 29, 34]¶

- Receive_Polarity_Recovery = 39¶

- Scratch_Register = 22¶

- Transmit_Negative_Width = 38¶

- Transmit_Positive_Width = 37¶

- USB_Interrupt_Enable_Falling = 16¶

- USB_Interrupt_Enable_Rising = 13¶

- USB_Interrupt_Latch = 20¶

- USB_Interrupt_Status = 19¶

- Vendor_ID_High = 1¶

- Vendor_ID_Low = 0¶

- class hwtLib.peripheral.usb.usb2.ulpi.ULPI_TX_CMD[source]¶

Bases:

object- EXTR = 239¶

- EXTW = 175¶

- Variables

REGR – Register read command with 6-bit immediate address.

- NOOP = 0¶

- Variables

NOOP – Transmit USB data that does not have a USB_PID, such as chirp and resume signalling. The PHY starts transmitting on the USB beginning with the next data byte.

- NOPID = 64¶

- class hwtLib.peripheral.usb.usb2.ulpi.Ulpi(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

InterfaceULPI (UTMI+ Low Pin Interface for USB2.0 PHY)

- Variables

~.data – Bi-directional data bus, driven low by the Link during idle. Bus ownership is determined by dir. The Link and PHY initiate data transfers by driving a non-zero pattern onto the data bus. LPI defines interface timing for single-edge data transfers with respect to rising edge of clock. An implementation may optionally define double-edge data transfers with respect to both rising and falling edges of clock.

~.dir – Direction. Controls the direction of the data bus. When the PHY has data to transfer to the Link, it drives dir high to take ownership of the bus. When the PHY has no data to transfer it drives dir low and monitors the bus for Link activity. The PHY pulls dir high whenever the interface cannot accept data from the Link. For example, when the internal PHY PLL is not stable.

~.stp – Stop. The Link asserts this signal for 1 clock cycle to stop the data stream currently on the bus. If the Link is sending data to the PHY, stp indicates the last byte of data was on the bus in the previous cycle. If the PHY is sending data to the Link, stp forces the PHY to end its transfer, de-assert dir and relinquish control of the the data bus to the Link. (In the tx stp=1 is asserted after last word, data with stp=1 and after are interpreted as idle (until dir changes).)

~.nxt – Next. The PHY asserts this signal to throttle the data. When the Link is sending data to the PHY, nxt indicates when the current byte has been accepted by the PHY. The Link places the next byte on the data bus in the following clock cycle. When the PHY is sending data to the Link, nxt indicates when a new byte is available for the Link to consume. (In the rx nxt=0 means the transaction is paused and rx_cmd word is send instead of data.)

- HDL params

DATA_WIDTH - default value 8 of type int

- HDL IO

data - of type hwt.interfaces.tristate.TristateSig - SLAVE (Master=IN)

dir - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

stp - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

nxt - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

hwtLib.peripheral.usb.usb2.ulpi_agent module¶

- class hwtLib.peripheral.usb.usb2.ulpi_agent.UlpiAgent(sim: HdlSimulator, intf: Ulpi, allowNoReset=False)[source]¶

Bases:

SyncAgentBaseAgent for

hwtLib.peripheral.usb.usb2.ulpi.Ulpiinterface. It allows for receiving and transmitting raw data over ULPI, it does not implement USB stack.- Note

the RX is always from PHY to Link, the TX is always from Link to PHY

- Note

in link->phy nxt works as a handshake ready and stp as handshake valid_n and data is data.o

- :note in phy->link nxt works as a handshake valid (but when set to 0 rx_cmd is send instead of data)

and the stp works as handshake ready_n, if stp is set to 1 the transmission of whole packet is interrupted.

- __init__(sim: HdlSimulator, intf: Ulpi, allowNoReset=False)[source]¶

- Parameters

rst – tuple (rst signal, rst_negated flag)

- driver()[source]¶

Drive ULPI interface as a PHY (and host) does

Inputs:

data.t (should be 0 in rx and turnaround else mask(8))

data.o (only in tx, 1st byt is cmd, rest is data)

stp (1 for 1 clk after last word in tx)

Outputs:

data.i (None in tx, else depending on nxt)

dir

nxt (0 if tx should stall or rx is stalled and sending rxd cmd instead)

hwtLib.peripheral.usb.usb2.ulpi_usb_agent module¶

- class hwtLib.peripheral.usb.usb2.ulpi_usb_agent.UlpiUsbAgent(sim: HdlSimulator, intf: Ulpi, allowNoReset=False)[source]¶

Bases:

UlpiAgenthwtLib.peripheral.usb.usb2.ulpi_agent.UlpiAgentwith device host logic and USB stack- __init__(sim: HdlSimulator, intf: Ulpi, allowNoReset=False)[source]¶

- Parameters

rst – tuple (rst signal, rst_negated flag)

- driver()[source]¶

Drive ULPI interface as a PHY (and host) does

Inputs:

data.t (should be 0 in rx and turnaround else mask(8))

data.o (only in tx, 1st byt is cmd, rest is data)

stp (1 for 1 clk after last word in tx)

Outputs:

data.i (None in tx, else depending on nxt)

dir

nxt (0 if tx should stall or rx is stalled and sending rxd cmd instead)

- getMonitors()[source]¶

Called before simulation to collect all monitors of interfaces from this agent

- class hwtLib.peripheral.usb.usb2.ulpi_usb_agent.UlpiUsbDevProcAgent(rx: Deque[Union[UsbPacketToken, UsbPacketData]], tx: Deque[Union[UsbPacketToken, UsbPacketData]], descriptors: UsbDescriptorBundle)[source]¶

Bases:

UsbDevAgent- deparse_packet(p: Union[UsbPacketToken, UsbPacketData, UsbPacketHandshake])[source]¶

Called to convert the packet from types supported by this class before putting into tx/rx queue

- class hwtLib.peripheral.usb.usb2.ulpi_usb_agent.UlpiUsbHostProcAgent(rx: Deque[Union[UsbPacketToken, UsbPacketData, UsbPacketHandshake]], tx: Deque[Union[UsbPacketToken, UsbPacketData, UsbPacketHandshake]])[source]¶

Bases:

UtmiUsbHostProcAgentA simulation agent for

hwtLib.peripheral.usb.usb2.ulpi.Ulpiinterface with the functionality of the host.- deparse_packet(p: Union[UsbPacketToken, UsbPacketData, UsbPacketHandshake])[source]¶

Called to convert the packet from types supported by this class before putting into tx/rx queue

hwtLib.peripheral.usb.usb2.utmi module¶

- class hwtLib.peripheral.usb.usb2.utmi.Utmi_8b(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

InterfaceUTMI+ (USB 2.0 Transceiver Macrocell Interace) Level 3, 8b variant only

https://www.intel.com/content/dam/www/public/us/en/documents/technical-specifications/usb2-transceiver-macrocell-interface-specification.pdf http://ww1.microchip.com/downloads/en/DeviceDoc/00002142A.pdf

- HDL IO

LineState - of type hwt.interfaces.std.Signal with dtype=<Bits, 2bits> - MASTER

function_control - of type hwt.interfaces.structIntf.StructIntf with dtype=struct { <Bits, 2bits> XcvrSelect <Bits, 1bit> TermSelect <Bits, 2bits> OpMode <Bits, 1bit> Reset <Bits, 1bit> SuspendM //<Bits, 1bit> empty space } - SLAVE (Master=IN)

otg_control - of type hwt.interfaces.structIntf.StructIntf with dtype=struct { <Bits, 1bit> IdPullup <Bits, 1bit> DpPulldown <Bits, 1bit> DmPulldown <Bits, 1bit> DischrgVbus <Bits, 1bit> ChrgVbus <Bits, 1bit> DrvVbus <Bits, 1bit> DrvVbusExternal <Bits, 1bit> UseExternalVbusIndicator } - SLAVE (Master=IN)

interrupt - of type hwt.interfaces.structIntf.StructIntf with dtype=struct { <Bits, 1bit> HostDisconnect <Bits, 1bit> VbusValid <Bits, 1bit> SessValid <Bits, 1bit> SessEnd <Bits, 1bit> IdGnd //<Bits, 3bits> empty space } - MASTER

tx - of type hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_tx - SLAVE (Master=IN)

rx - of type hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_rx - MASTER

- class hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_rx(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

VldSynced

- HDL params

DATA_WIDTH - default value 8 of type int

- HDL IO

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

valid - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

active - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

error - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

- class hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_tx(masterDir=DIRECTION.OUT, hdl_name: Optional[Union[str, Dict[str, str]]] = None, loadConfig=True)[source]¶

Bases:

Handshaked

- HDL params

DATA_WIDTH - default value 8 of type int

- HDL IO

data - of type hwt.interfaces.std.Signal with dtype=<Bits, 8bits> - MASTER

vld - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - MASTER

rd - of type hwt.interfaces.std.Signal with dtype=<Bits, 1bit> - SLAVE (Master=IN)

hwtLib.peripheral.usb.usb2.utmi_agent module¶

- class hwtLib.peripheral.usb.usb2.utmi_agent.Utmi_8bAgent(sim: HdlSimulator, intf: Utmi_8b)[source]¶

Bases:

AgentBaseSimulation agent for

hwtLib.peripheral.usb.usb2.utmi.Utmi_8binterface.- property actual_link_to_phy_packet¶

- property actual_link_to_phy_packet_setter¶

- property actual_phy_to_link_packet¶

- property actual_phy_to_link_packet_setter¶

- getMonitors()[source]¶

Called before simulation to collect all monitors of interfaces from this agent

- property link_to_phy_packets¶

- property link_to_phy_packets_setter¶

- property phy_to_link_packets¶

- property phy_to_link_packets_setter¶

- class hwtLib.peripheral.usb.usb2.utmi_agent.Utmi_8b_rxAgent(sim: HdlSimulator, intf: Utmi_8b_rx, allowNoReset=False)[source]¶

Bases:

SyncAgentBaseSimulation agent for

hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_rxinterface.- Attention

“active” signal acts as a valid, “valid” signal acts as a mask

- Variables

data – Deque[Deque[Tuple[int, int]]] (internal deque represents packets, tuple represents data, error)

- USB_ERROR = 'ERROR'¶

- __init__(sim: HdlSimulator, intf: Utmi_8b_rx, allowNoReset=False)[source]¶

- Parameters

rst – tuple (rst signal, rst_negated flag)

- class hwtLib.peripheral.usb.usb2.utmi_agent.Utmi_8b_txAgent(sim: HdlSimulator, intf, allowNoReset=False)[source]¶

Bases:

SyncAgentBaseSimulation agent for

hwtLib.peripheral.usb.usb2.utmi.Utmi_8b_txinterface.- Variables

data – Deque[Deque[int]] (internal deque represents packets)

hwtLib.peripheral.usb.usb2.utmi_to_ulpi module¶

- class hwtLib.peripheral.usb.usb2.utmi_to_ulpi.Utmi_to_Ulpi(hdl_name_override: Optional[str] = None)[source]¶

Bases:

UnitThe ULPI is an interface which reduces the number of signals for UTMI+ interface. This reduction is done using a register file which drives signals which are not used and bi-directional wiring. This component does translation of ULPI to UTMI+ by keeping copy of UTMI+ registers and synchronizing the changes and it also handles the drive of the bi-directional wires.

- HDL IO

clk - of type hwt.interfaces.std.Clk with dtype=<Bits, 1bit> - SLAVE

rst - of type hwt.interfaces.std.Rst with dtype=<Bits, 1bit> - SLAVE

utmi - of type hwtLib.peripheral.usb.usb2.utmi.Utmi_8b - MASTER

ulpi - of type hwtLib.peripheral.usb.usb2.ulpi.Ulpi - SLAVE

hwtLib.peripheral.usb.usb2.utmi_usb_agent module¶

- class hwtLib.peripheral.usb.usb2.utmi_usb_agent.UtmiUsbAgent(sim: HdlSimulator, intf: Utmi_8bAgent, allowNoReset=False)[source]¶

Bases:

Utmi_8bAgent,SyncAgentBase:class:` hwtLib.peripheral.usb.usb2.utmi_agent.Utmi_8bAgent` with device host logic and USB stack

- __init__(sim: HdlSimulator, intf: Utmi_8bAgent, allowNoReset=False)[source]¶

- Parameters

rst – tuple (rst signal, rst_negated flag)

- class hwtLib.peripheral.usb.usb2.utmi_usb_agent.UtmiUsbDevProcAgent(rx: Deque[Union[UsbPacketToken, UsbPacketData]], tx: Deque[Union[UsbPacketToken, UsbPacketData]], descriptors: UsbDescriptorBundle)[source]¶

Bases:

UsbDevAgent- deparse_packet(p)[source]¶

Called to convert the packet from types supported by this class before putting into tx/rx queue

- class hwtLib.peripheral.usb.usb2.utmi_usb_agent.UtmiUsbHostProcAgent(rx: Deque[Union[UsbPacketToken, UsbPacketData, UsbPacketHandshake]], tx: Deque[Union[UsbPacketToken, UsbPacketData, UsbPacketHandshake]])[source]¶

Bases:

UsbHostAgentA simulation agent for

hwtLib.peripheral.usb.usb2.utmi.Utmi_8binterface with the functionality of the host.- deparse_packet(p: Union[UsbPacketToken, UsbPacketData, UsbPacketHandshake])[source]¶

Called to convert the packet from types supported by this class before putting into tx/rx queue

- parse_packet(p: Deque[int])[source]¶

Called to convert the packet from tx/rx queues to types supported by this class

- usb_packet_token_t = struct { <Bits, 4bits> pid <Bits, 4bits> pid_inv <Bits, 7bits> addr <Bits, 4bits> endp <Bits, 5bits> crc5 }¶